## (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2019/0347990 A1

Nov. 14, 2019 (43) Pub. Date:

## (54) MEMORY-IN-PIXEL ARCHITECTURE

## Applicant: Apple Inc., Cupertino, CA (US)

(72) Inventors: **Ivan Knez**, San Jose, CA (US); Tien-Chien Kuo, Sunnyvale, CA (US); Yingkan Lin, San Jose, CA (US); Bilin Wang, Santa Clara, CA (US); Kanghoon Jeon, Albany, CA (US); Mitchell Herman Kline, Alameda, CA (US); Hopil Bae, Palo Alto, CA (US); Jose Antonio Dominguez-Caballero, San Jose, CA (US); Chun-Yao Huang, San Jose, CA (US); Syed Farhan Mohiuddin, Santa Clara, CA (US)

(21) Appl. No.: 16/399,792

(22) Filed: Apr. 30, 2019

## Related U.S. Application Data

(60) Provisional application No. 62/668,707, filed on May 8, 2018.

### **Publication Classification**

(51) Int. Cl. G09G 3/3233 (2006.01)G04G 9/10 (2006.01)G06F 1/16 (2006.01)

(52) U.S. Cl. CPC ... G09G 3/3233 (2013.01); G09G 2300/0842

(2013.01); G06F 1/1637 (2013.01); G04G 9/102 (2013.01)

#### (57)ABSTRACT

An electronic display may include an active area having a first pixel formed in the active area, where the first pixel emits light in response to image data. The electronic display may also include a controller to transmit the image data to the first pixel. The first pixel may include an organic light-emitting diode that emits the light in response to the image data, memory to digitally store the image data received from the controller, and driver circuitry to receive the image data from the memory. The driver circuitry may cause the organic light-emitting diode to emit the light in response to the image data.

FIG. 18

FIG. 19

FIG. 22

## MEMORY-IN-PIXEL ARCHITECTURE

## CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims priority to U.S. Provisional Patent Application No. 62/668,707, entitled "MEMORY-IN-PIXEL ARCHITECTURE," filed on May 8, 2018, which is incorporated herein by reference in its entirety for all purposes.

### **SUMMARY**

[0002] A summary of certain embodiments disclosed herein is set forth below. It should be understood that these aspects are presented merely to provide the reader with a brief summary of these certain embodiments and that these aspects are not intended to limit the scope of this disclosure. Indeed, this disclosure may encompass a variety of aspects that may not be set forth below.

[0003] Methods and systems for reducing bandwidths, or amounts simultaneously transmitted, of image data transmitted and processed to prepare an image for presentation on an electronic display by implementing memory in pixels of the electronic display may provide immense value. Such an implementation of memory in the pixels may permit an elimination of a frame buffer associated with the electronic display. Having memory in the pixels may lessen the design complexity of electronic displays, as well, because the less image data that is concurrently transmitted to a pixel array of an electronic display, the simpler an electronic display may be designed. For example, the pixels may be programmed in smaller groups because memory in the pixel stores the values until a time of presentation of the image. [0004] This disclosure describes an electronic display having one or more pixels that include memory and a driver that may help to decrease a bandwidth associated with transmitting and processing image data for presentation on an electronic display. The inclusion of the memory in the pixel may enable storage of image data prior to output to a light-emitting portion of the pixel. Thus, the memory in the pixel may reduce, or in some instances eliminate, a reliance upon a frame buffer in an electronic display by acting as an individual frame buffer for the pixel. The memory in the pixel may be used in conjunction with a driver to cause a light-emitting portion of the pixel to emit light.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0005] Various aspects of this disclosure may be better understood upon reading the following detailed description and upon reference to the drawings in which:

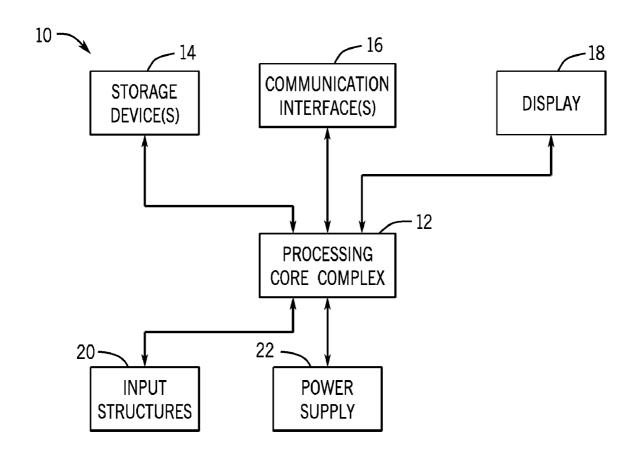

[0006] FIG. 1 is a schematic block diagram of an electronic device, in accordance with an embodiment;

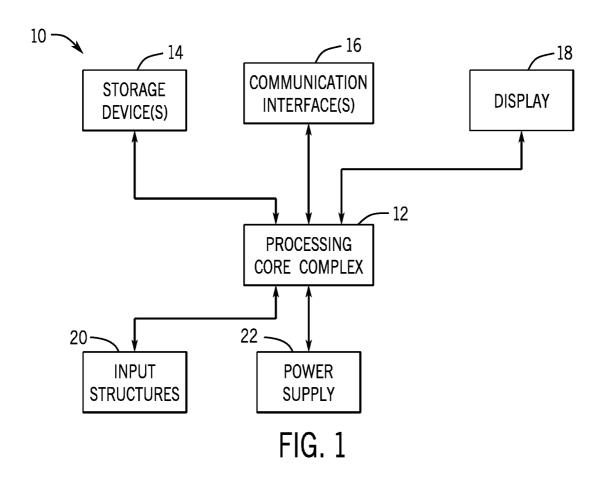

[0007] FIG. 2 is a perspective view of a watch representing an embodiment of the electronic device of FIG. 1, in accordance with an embodiment;

[0008] FIG. 3 is a front view of a tablet device representing an embodiment of the electronic device of FIG. 1, in accordance with an embodiment;

[0009] FIG. 4 is a front view of a computer representing an embodiment of the electronic device of FIG. 1, in accordance with an embodiment:

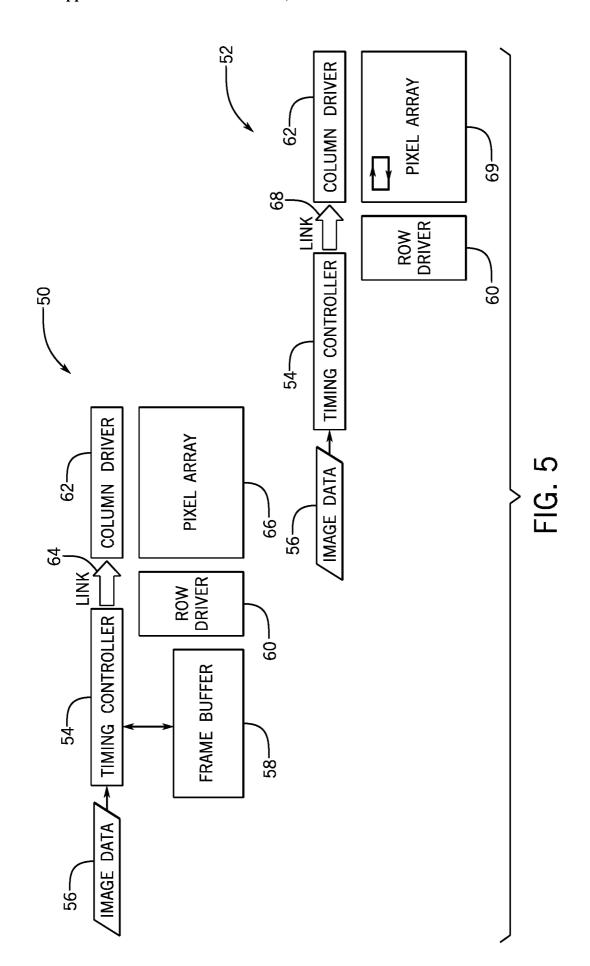

[0010] FIG. 5 is a block diagram of a display system of the electronic device of FIG. 1, in accordance with an embodiment;

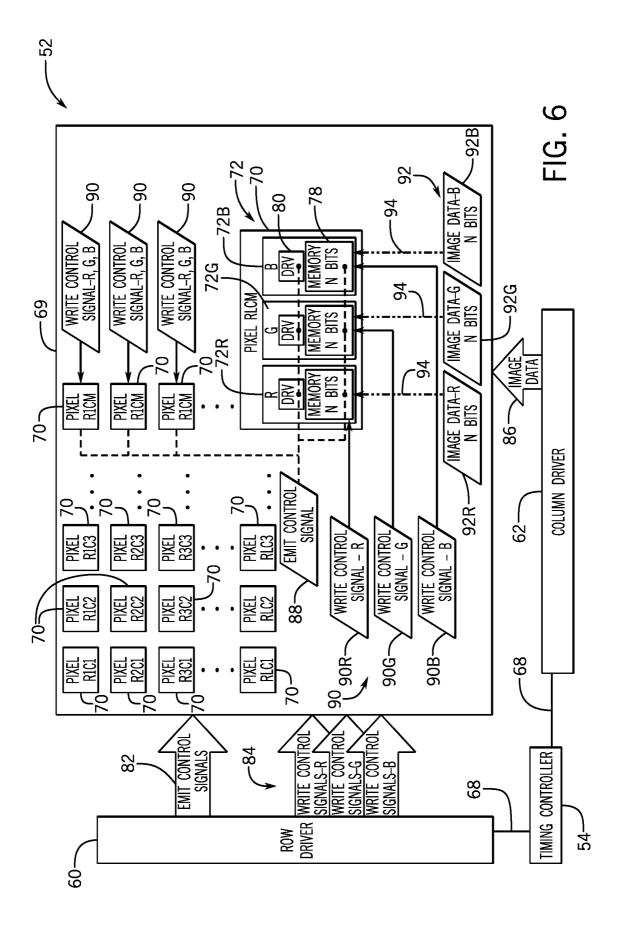

[0011] FIG. 6 is a block diagram of a pixel array of the display system of FIG. 5, in accordance with an embodiment;

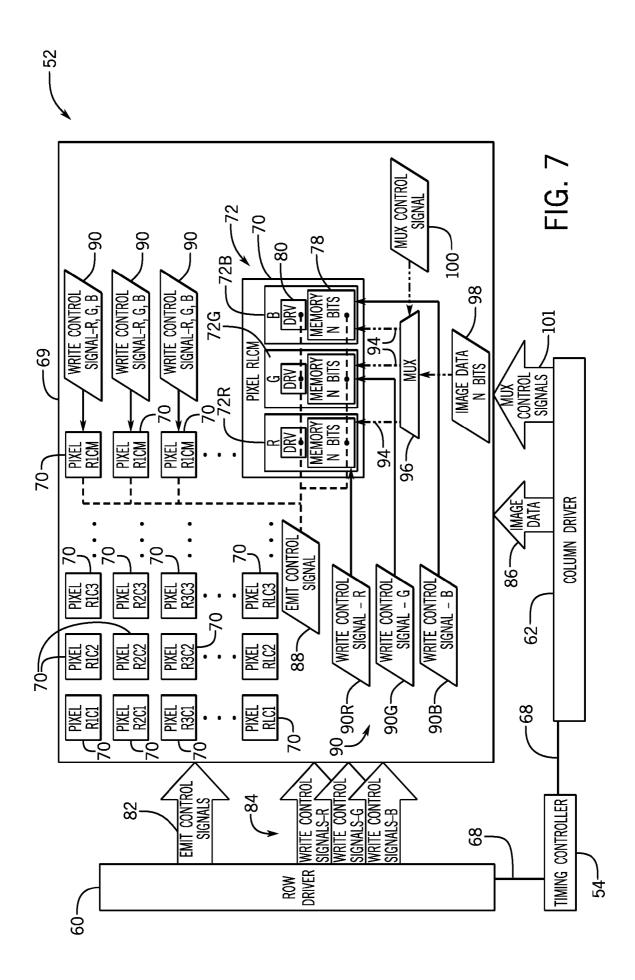

[0012] FIG. 7 is a block diagram of an embodiment of the pixel array of FIG. 6, in accordance with an embodiment; [0013] FIG. 8 is a block diagram of a pixel of the pixel array of FIG. 6 that emits light according to a binary pulse width modulation emission scheme, in accordance with an

embodiment; [0014] FIG. 9 is a block diagram of an embodiment of the pixel of the pixel array of FIG. 6 that emits light according to a single pulse width modulation emission scheme, in accordance with an embodiment;

[0015] FIG. 10 is a block diagram of another embodiment of the pixel of the pixel array of FIG. 6 that emits light according to a pulse density modulation emission scheme, in accordance with an embodiment:

[0016] FIG. 11 is a timing diagram of programming sequences performed by a column driver of the display system of FIG. 5, in accordance with an embodiment;

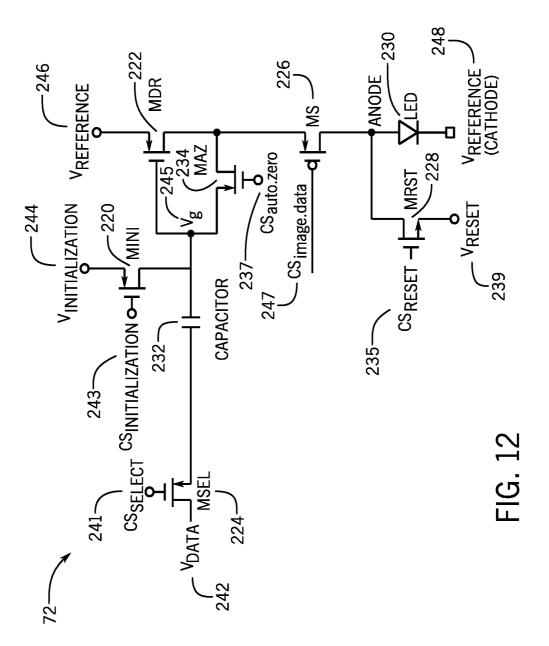

[0017] FIG. 12 is a circuit diagram of a first embodiment of a sub-pixel of the pixel array of FIG. 6 having a current drive, in accordance with an embodiment;

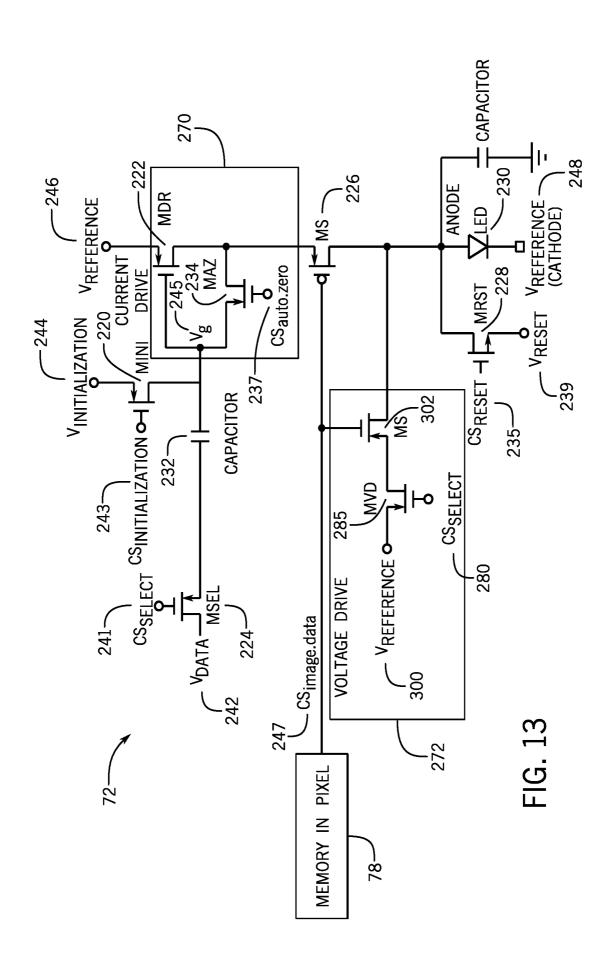

[0018] FIG. 13 is a circuit diagram of a second embodiment of the sub-pixel of the pixel array of FIG. 6 having a hybrid drive and having memory, in accordance with an embodiment:

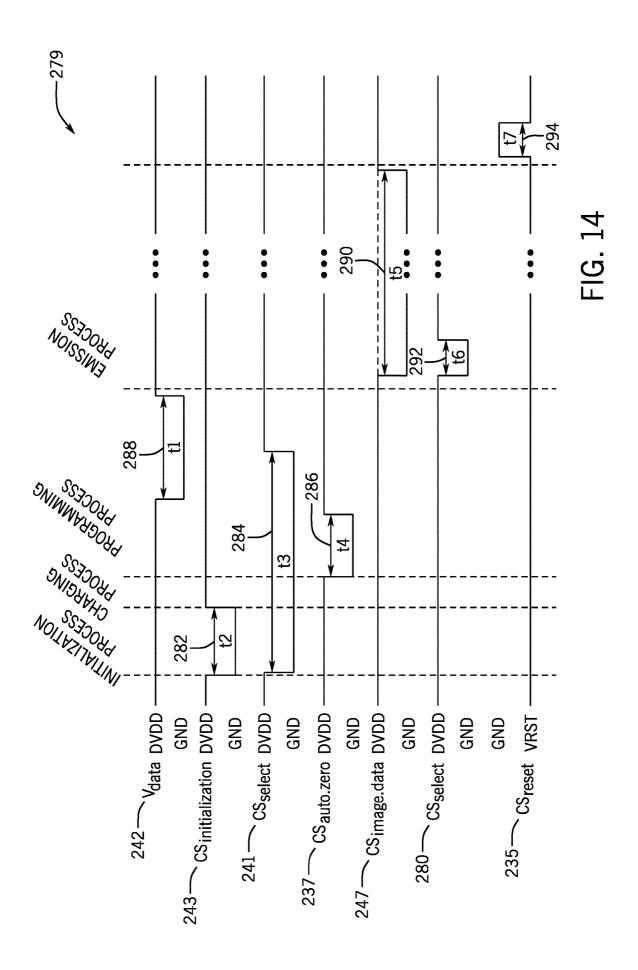

[0019] FIG. 14 is a timing diagram of control signals used to operate the sub-pixel of FIG. 13 to display an image, in accordance with an embodiment;

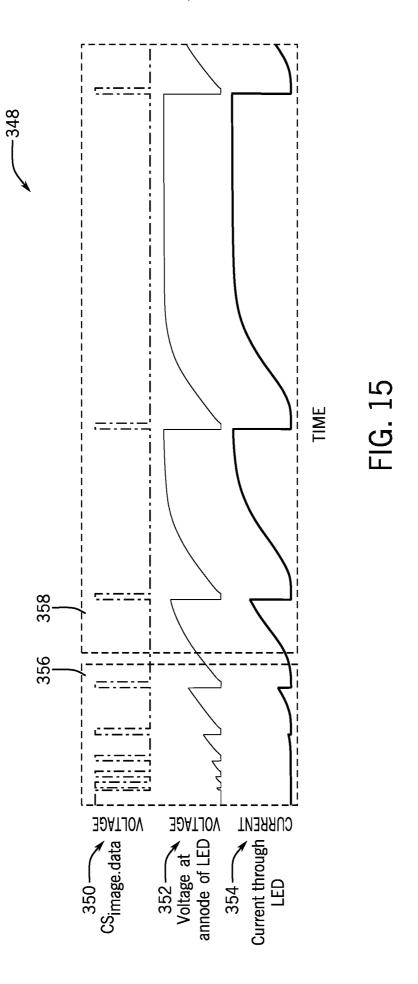

[0020] FIG. 15 is a graph showing a current and a voltage created by simulating transmission of image data corresponding to a binary pulse width modulated emission scheme to the sub-pixel of FIG. 12, in accordance with an embodiment;

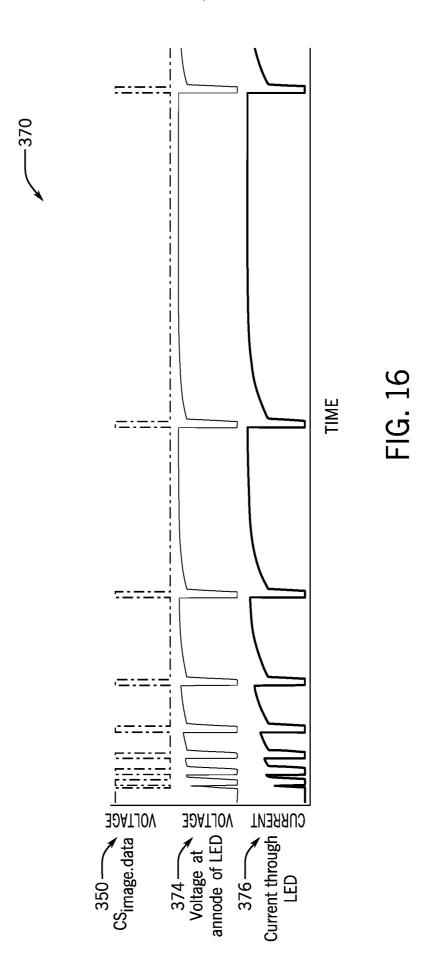

[0021] FIG. 16 is a graph showing a current and a voltage created by simulating transmission of image data corresponding to a binary pulse width modulated emission scheme to the sub-pixel of FIG. 13, in accordance with an embodiment;

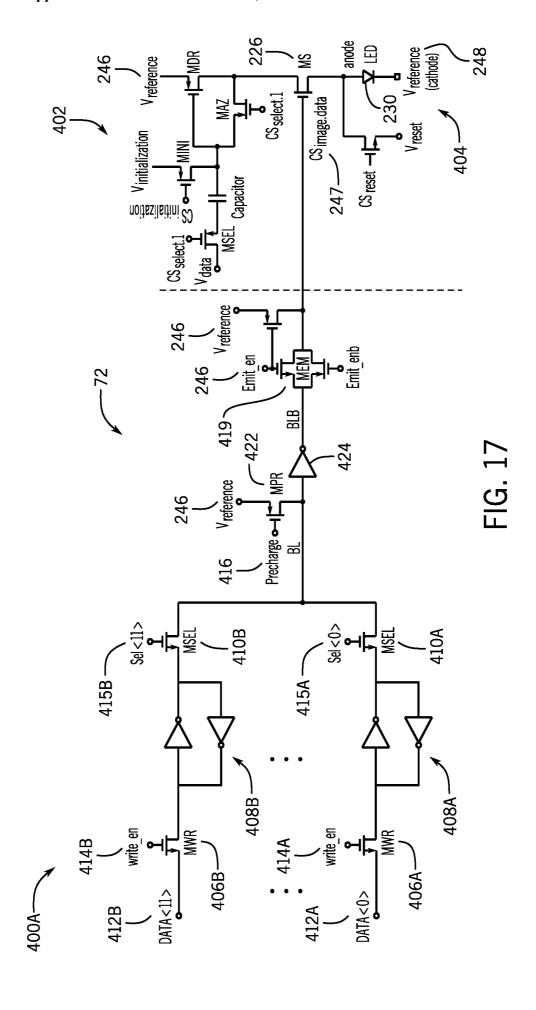

[0022] FIG. 17 is a circuit diagram of memory circuitry coupled to the sub-pixel of FIG. 12, in accordance with an embodiment:

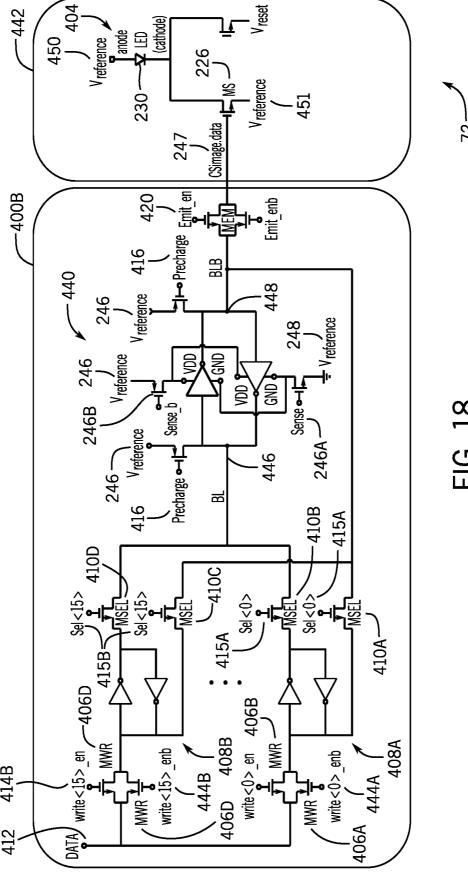

[0023] FIG. 18 is a circuit diagram of an embodiment of the memory circuitry of FIG. 17 coupled to an embodiment of a sub-pixel of FIG. 12 implementing a global anode, in accordance with an embodiment;

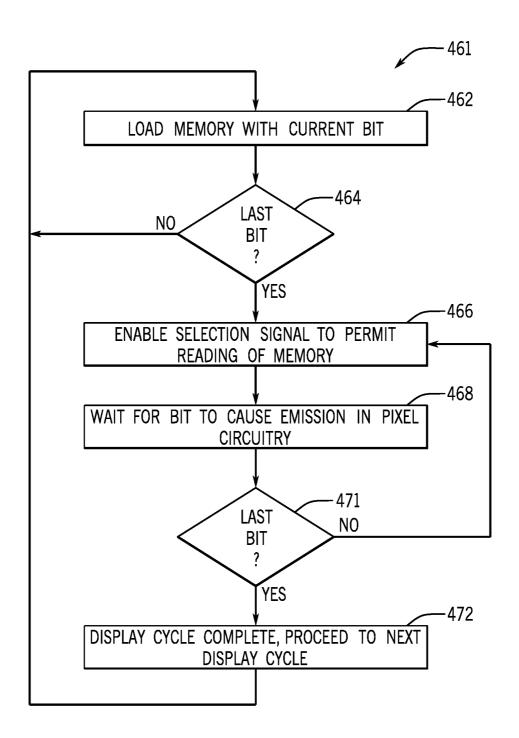

[0024] FIG. 19 is a process for operating the sub-pixel of FIG. 18, in accordance with an embodiment;

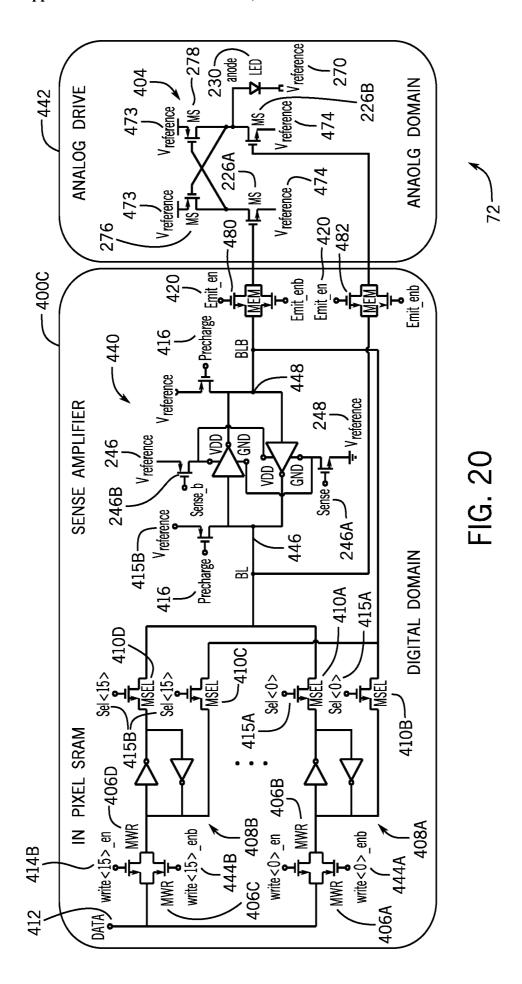

[0025] FIG. 20 is a circuit diagram of an embodiment of the sub-pixel of FIG. 18 implementing a global cathode, in accordance with an embodiment;

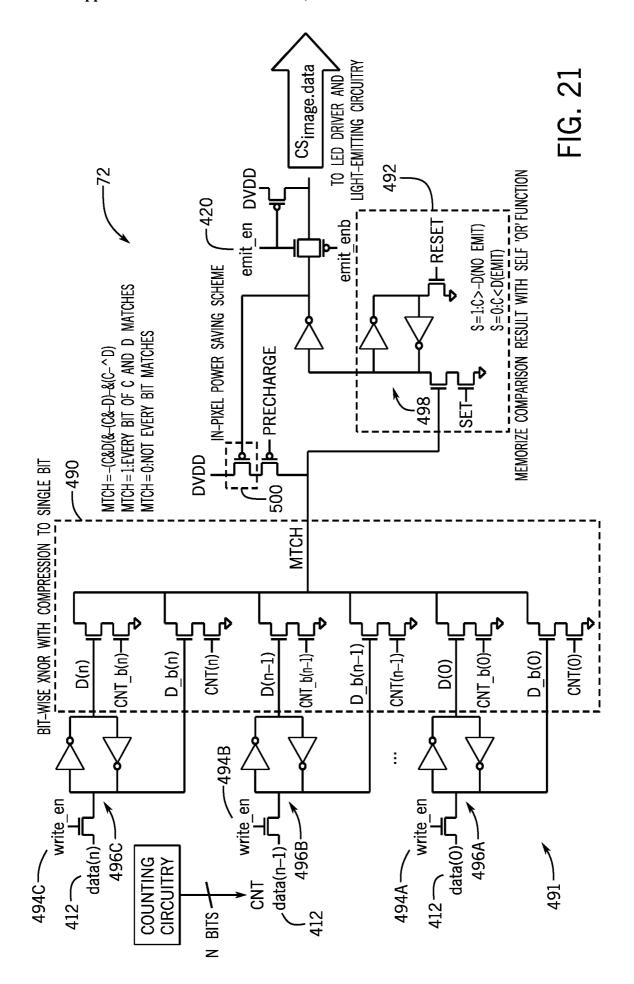

[0026] FIG. 21 is a circuit diagram of an embodiment of the memory circuitry of FIG. 13, in accordance with an embodiment;

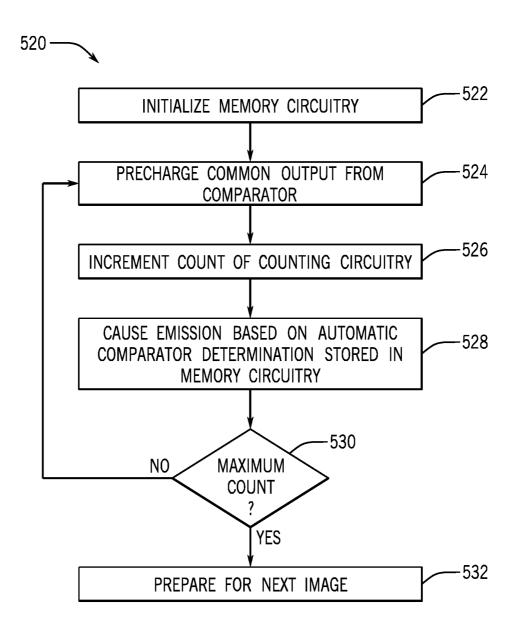

[0027] FIG. 22 is a process for operating the memory circuitry of FIG. 21, in accordance with an embodiment;

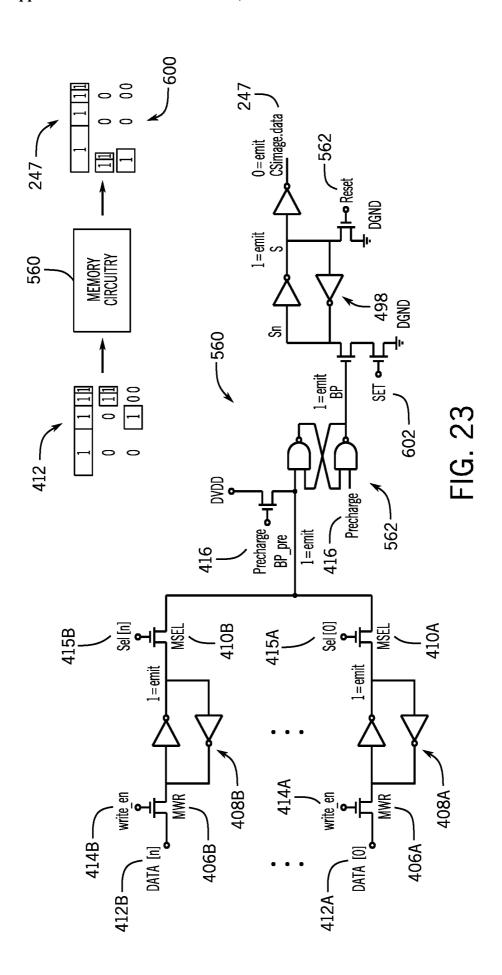

[0028] FIG. 23 is a circuit diagram of an embodiment of the memory circuitry of FIG. 13, in accordance with an embodiment;

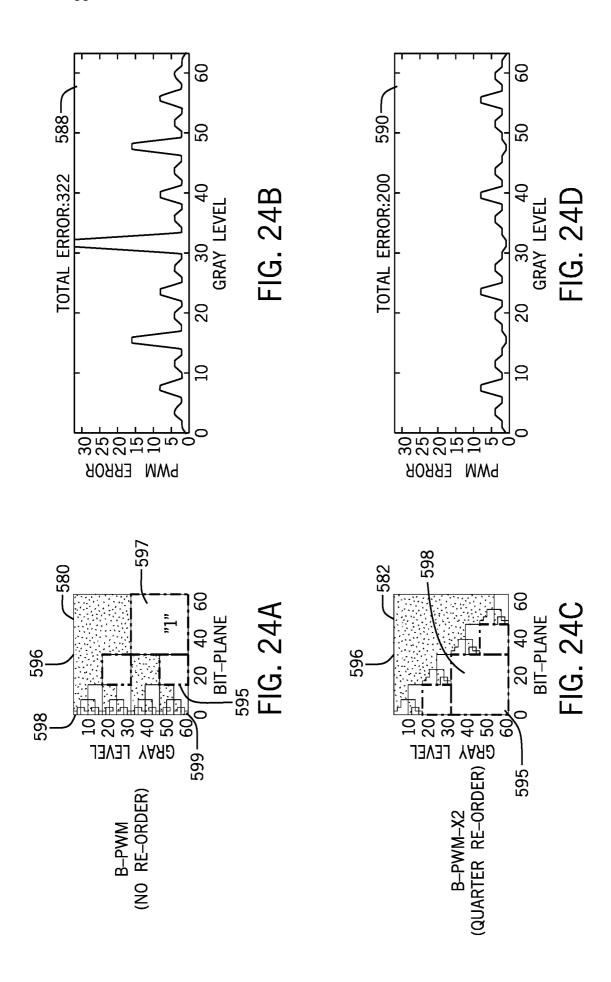

[0029] FIG. 24A is a bit-plane graph corresponding to no reordering implemented in the memory circuitry of FIG. 23, in accordance with an embodiment;

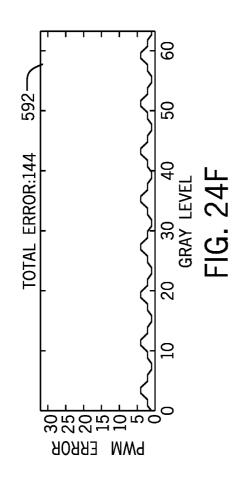

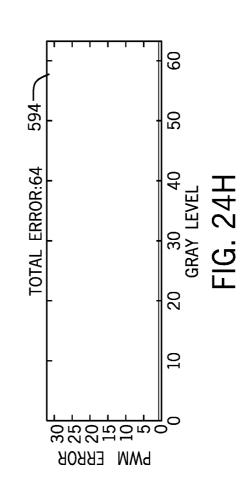

[0030] FIG. 24B is an error graph corresponding to no reordering implemented in the memory circuitry of FIG. 23, in accordance with an embodiment;

[0031] FIG. 24C is a bit-plane graph corresponding to two reorderings implemented in the memory circuitry of FIG. 23, in accordance with an embodiment;

[0032] FIG. 24D is an error graph corresponding to two reorderings implemented in the memory circuitry of FIG. 23. in accordance with an embodiment:

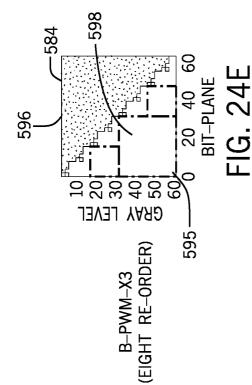

[0033] FIG. 24E is a bit-plane graph corresponding to three reorderings implemented in the memory circuitry of FIG. 23, in accordance with an embodiment;

[0034] FIG. 24F is an error graph corresponding to three reorderings implemented in the memory circuitry of FIG. 23, in accordance with an embodiment;

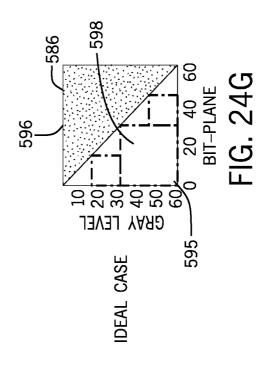

[0035] FIG. 24G is a bit-plane graph corresponding to an ideal case of reordering implemented in the memory circuitry of FIG. 23, in accordance with an embodiment;

[0036] FIG. 24H is an error graph corresponding to an ideal case of reordering implemented in the memory circuitry of FIG. 23, in accordance with an embodiment;

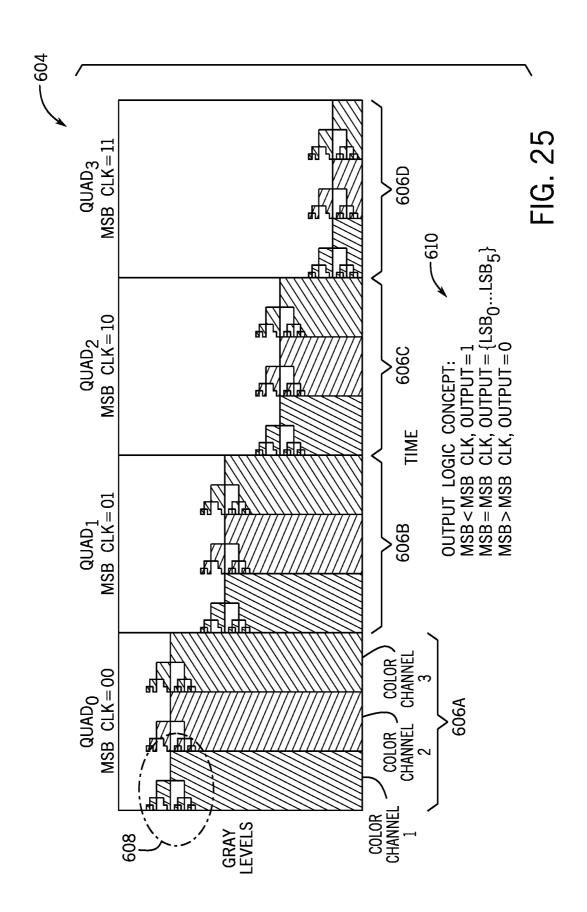

[0037] FIG. 25 is a bit-plane graph illustrating the bitplane graph of FIG. 24C over time and with an inclusion of additional color channels, in accordance with an embodiment:

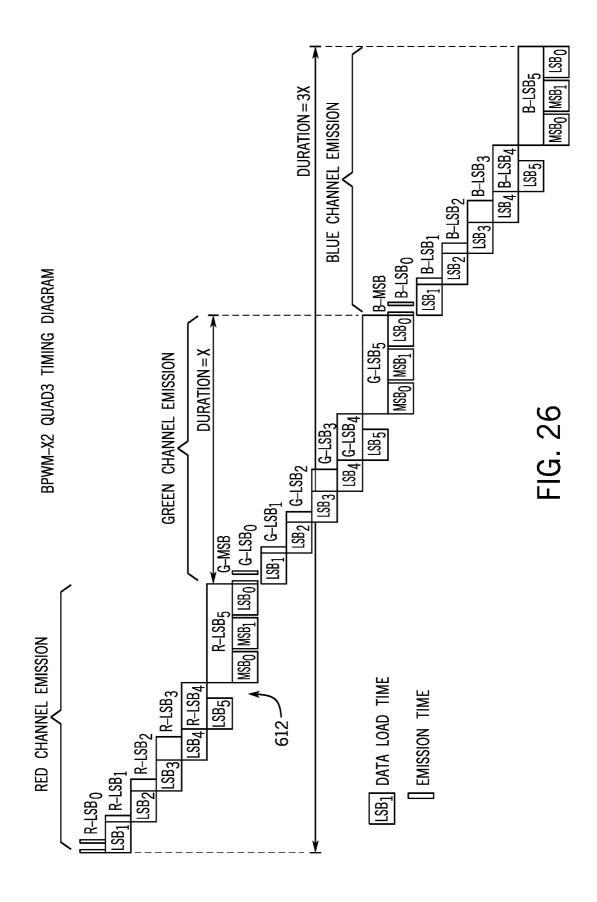

[0038] FIG. 26 is a timing diagram illustrating a loading and emission process associated with a third quadrant of the bit-plane graph of FIG. 25, in accordance with an embodiment:

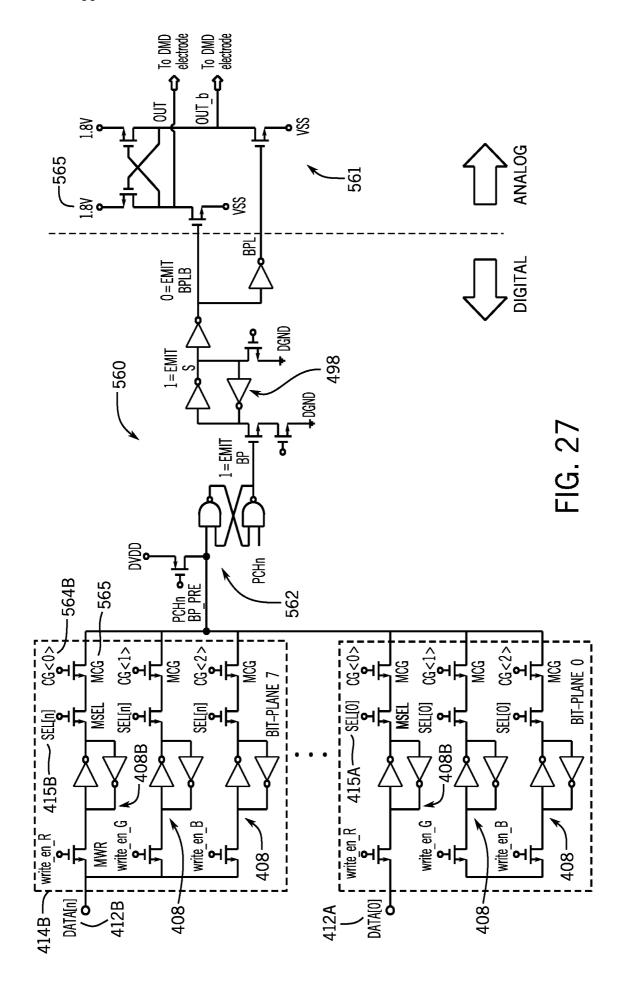

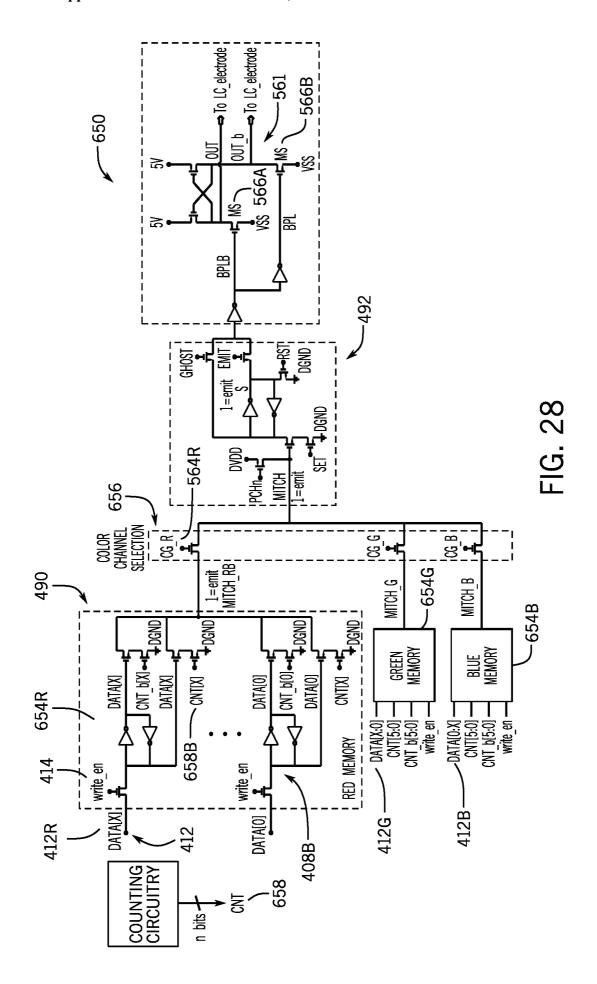

[0039] FIG. 27 is a circuit diagram of an embodiment of the memory circuitry of FIG. 23 implemented for use in a digital mirror display, in accordance with an embodiment; [0040] FIG. 28 is a circuit diagram of an embodiment of the pixel of FIG. 25 for use in a liquid crystal display, in accordance with an embodiment;

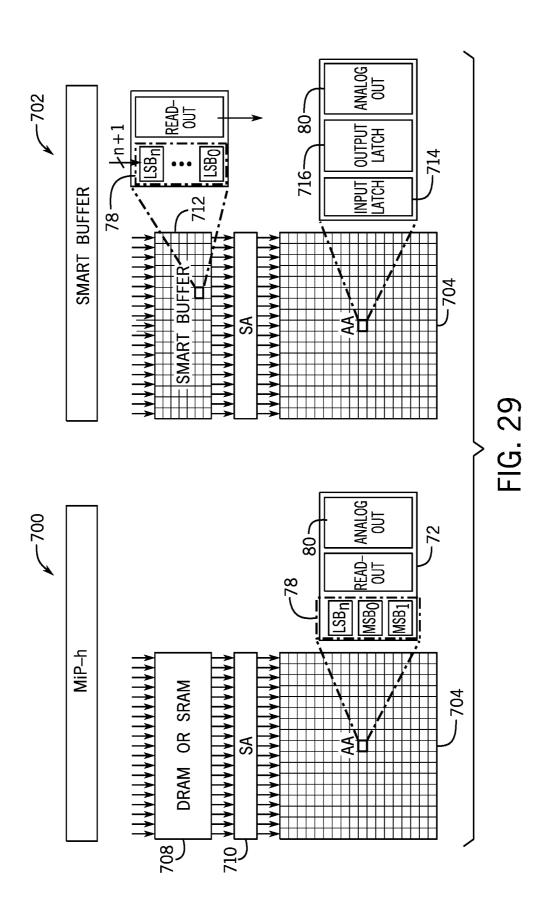

[0041] FIG. 29 is a block diagram comparing the display system of FIG. 5 with a display system having a smart buffer outside of an active area of the electronic display, in accordance with an embodiment:

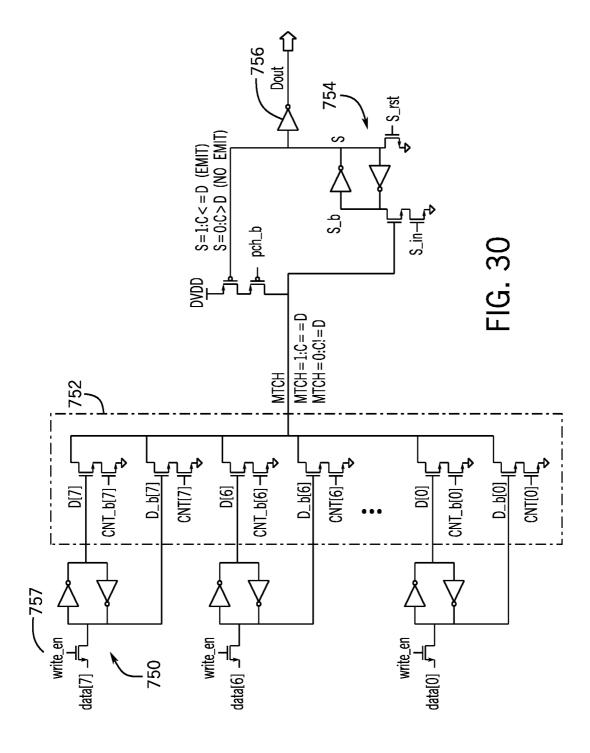

[0042] FIG. 30 is a circuit diagram of an embodiment of the memory circuitry of FIG. 13 for use in the smart buffer of FIG. 29, in accordance with an embodiment; and

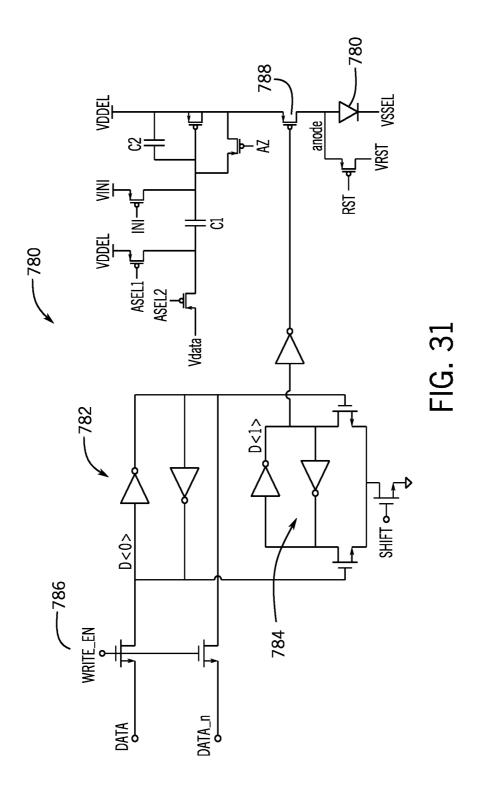

[0043] FIG. 31 is a circuit diagram of a third embodiment of sub-pixel of the pixel array of FIG. 6 for use in the display system having the smart buffer of FIG. 29, in accordance with an embodiment.

## DETAILED DESCRIPTION OF SPECIFIC EMBODIMENTS

[0044] One or more specific embodiments will be described below. In an effort to provide a concise description of these embodiments, not all features of an actual implementation are described in the specification. It should be appreciated that in the development of any such actual implementation, as in any engineering or design project, numerous implementation-specific decisions must be made to achieve the developers' specific goals, such as compliance with system-related and business-related constraints, which may vary from one implementation to another. Moreover, it should be appreciated that such a development effort might be complex and time consuming, but would nevertheless be a routine undertaking of design, fabrication, and manufacture for those of ordinary skill having the benefit of this disclosure.

[0045] When introducing elements of various embodiments of the present disclosure, the articles "a," "an," and "the" are intended to mean that there are one or more of the elements. The terms "comprising," "including," and "having" are intended to be inclusive and mean that there may be additional elements other than the listed elements. Additionally, it should be understood that references to "one embodiment" or "an embodiment" of the present disclosure are not intended to be interpreted as excluding the existence of additional embodiments that also incorporate the recited features.

[0046] Electronic displays are found in numerous electronic devices, from mobile phones to computers, televisions, automobile dashboards, and many more. Electronic displays have achieved increasingly higher resolutions by reducing individual pixel size. Yet increasing resolutions may increase a difficultly associated with managing an increased amount of image data associated with the increased resolutions processed by processing circuitry prior to displaying an image, for example, by causing increased power consumption from processing increased amounts of image data. Furthermore, the increasing resolutions may increase a bandwidth used to communicate image data from the processing circuitry to a pixel array for presentation of the image because more image data is used to communicate the same image at a higher electronic display resolution.

[0047] Embodiments of the present disclosure relate to systems and methods for implementing memory-in-pixel circuitry that may be used as an individual frame buffer for each pixel, which may reduce reliance on a frame buffer external to a pixel array and driving circuitry of an electronic display. Memory may be implemented in pixel circuitry that includes a light-emitting diode (LED). An organic light-emitting diode (OLED) represents one type of LED that may be found in the pixel, but other types of LEDs may also be used or light-emitting components may be used in the pixel circuitry, such as components to support liquid crystal displays (LCDs), plasma display panels, and/or dot-matrix displays.

[0048] The systems and methods of this disclosure to implement memory-in-pixel circuitry may reduce transmission bandwidths of image data to pixel arrays for display because the pixel may store image data in the memory. In this way, a reliance on frame buffers to temporarily store the image data external to the pixel is reduced because the pixel has its own memory to store its own image data prior to display of the image data.

[0049] A general description of suitable electronic devices that may include a self-emissive display, such as a LED (e.g., an OLED) display, and corresponding circuitry of this disclosure are provided. An OLED represents one type of LED that may be found in the self-emissive pixel, but other types of LEDs may also be used.

[0050] To help illustrate, an electronic device 10 including an electronic display 18 is shown in FIG. 1. As is described in more detail below, the electronic device 10 may be any suitable electronic device, such as a computer, a mobile phone, a portable media device, a tablet, a television, a virtual-reality headset, a vehicle dashboard, and the like. Thus, it should be noted that FIG. 1 is merely one example of a particular implementation and is intended to illustrate the types of components that may be present in an electronic device 10. The electronic device 10 may include, among other things, a processing core complex 12 such as a system

on a chip (SoC) and/or processing circuit(s), storage device (s) 14, communication interface(s) 16, the electronic display 18, input structures 20, and a power supply 22. The various components described in FIG. 1 may include hardware elements (e.g., circuitry), software elements (e.g., a tangible, non-transitory computer-readable medium storing instructions), or a combination of both hardware and software elements. It should be noted that the various depicted components may be combined into fewer components or separated into additional components.

[0051] As depicted, the processing core complex 12 is operably coupled with the storage device(s) 14. Thus, the processing core complex 12 execute instructions stored in the storage device(s) 14 to perform operations, such as generating and/or transmitting image data. As such, the processing core complex 12 may include one or more general purpose microprocessors, one or more application specific integrated circuits (ASICs), one or more field programmable logic arrays (FPGAs), or any combination thereof. Using pixels containing light-emitting components (e.g., LEDs, OLEDs), the electronic display 18 may show images generated by the processing core complex 12.

[0052] In addition to instructions, the storage device(s) 14 may store data to be processed by the processing core complex 12. Thus, in some embodiments, the storage device (s) 14 may include one or more tangible, non-transitory, computer-readable mediums. The storage device(s) 14 may be volatile and/or non-volatile. For example, the storage device(s) 14 may include random access memory (RAM) and/or read only memory (ROM), rewritable non-volatile memory such as flash memory, hard drives, optical discs, and/or the like, or any combination thereof.

[0053] As depicted, the processing core complex 12 is also operably coupled with the communication interface(s) 16. In some embodiments, the communication interface(s) 16 may facilitate communicating data with another electronic device and/or a network. For example, the communication interface (s) 16 (e.g., a radio frequency system) may enable the electronic device 10 to communicatively couple to a personal area network (PAN), such as a Bluetooth network, a local area network (LAN), such as an 1622.11x Wi-Fi network, and/or a wide area network (WAN), such as a 4G or Long-Term Evolution (LTE) cellular network.

[0054] Additionally, as depicted, the processing core complex 12 is also operably coupled to the power supply 22. In some embodiments, the power supply 22 may provide electrical power to one or more components in the electronic device 10, such as the processing core complex 12 and/or the electronic display 18. Thus, the power supply 22 may include any suitable source of energy, such as a rechargeable lithium polymer (Li-poly) battery and/or an alternating current (AC) power converter.

[0055] As depicted, the electronic device 10 is also operably coupled with the one or more input structures 20. In some embodiments, an input structure 20 may facilitate user interaction with the electronic device 10, for example, by receiving user inputs. Thus, the input structures 20 may include a button, a keyboard, a mouse, a trackpad, and/or the like. Additionally, in some embodiments, the input structures 20 may include touch-sensing components in the electronic display 18. In such embodiments, the touch sensing components may receive user inputs by detecting occurrence and/or position of an object touching the surface of the electronic display 18.

[0056] In addition to enabling user inputs, the electronic display 18 may include a display panel with one or more display pixels. As described above, the electronic display 18 may control light emission from the display pixels to present visual representations of information, such as a graphical user interface (GUI) of an operating system, an application interface, a still image, or video content, by displaying frames based at least in part on corresponding image data. As depicted, the electronic display 18 is operably coupled to the processing core complex 12. In this manner, the electronic display 18 may display frames based at least in part on image data generated by the processing core complex 12. Additionally or alternatively, the electronic display 18 may display frames based at least in part on image data received via the communication interface(s) 16 and/or the input structures 20.

[0057] As may be appreciated, the electronic device 10 may take a number of different forms. As shown in FIG. 2, the electronic device 10 may take the form of a watch 30. For illustrative purposes, the watch 30 may be any Apple Watch® model available from Apple Inc. As depicted, the watch 30 includes an enclosure 32 (e.g., housing). In some embodiments, the enclosure 32 may protect interior components from physical damage and/or shield them from electromagnetic interference (e.g., house components). A strap 34 may enable the watch 30 to be worn on the arm or wrist. The electronic display 18 may display information related to the operation of the watch 30. Input structures 20 may enable the user to activate or deactivate watch 30, navigate a user interface to a home screen, navigate a user interface to a user-configurable application screen, activate a voice-recognition feature, provide volume control, and/or toggle between vibrate and ring modes. As depicted, the input structures 20 may be accessed through openings in the enclosure 32. In some embodiments, the input structures 20 may include, for example, an audio jack to connect to external devices.

[0058] The electronic device 10 may also take the form of a tablet device 40, as shown in FIG. 3. For illustrative purposes, the tablet device 40 may be any iPad® model available from Apple Inc. Depending on the size of the tablet device 40, the tablet device 40 may serve as a handheld device such as a mobile phone. The tablet device 40 includes an enclosure 42 through which input structures 20 may protrude. In certain examples, the input structures 20 may include a hardware keypad (not shown). The enclosure 42 also holds the electronic display 18. The input structures 20 may enable a user to interact with a GUI of the tablet device 40. For example, the input structures 20 may enable a user to type a Rich Communication Service (RCS) text message, a Short Message Service (SMS) text message, or make a telephone call. A speaker 44 may output a received audio signal and a microphone 46 may capture the voice of the user. The tablet device 40 may also include a communication interface 16 to enable the tablet device 40 to connect via a wired connection to another electronic device.

[0059] FIG. 4 illustrates a computer 48, which represents another form that the electronic device 10 may take. For illustrative purposes, the computer 48 may be any Macbook® or iMac® model available from Apple Inc. It should be appreciated that the electronic device 10 may also take the form of any other computer, including a desktop computer. The computer 48 shown in FIG. 4 includes the electronic display 18 and input structures 20 that include a

keyboard and a track pad. Communication interfaces 16 of the computer 48 may include, for example, a universal service bus (USB) connection.

[0060] In any case, as described above, operating an electronic device 10 to communicate information by displaying images on its electronic display 18 generally consumes electrical power. Additionally, as described above, electronic devices 10 often store a finite amount of electrical energy. Thus, to facilitate improving power consumption efficiency, an electronic device 10, in some embodiments, may include an electronic display 18 that implements memory-in-pixel as a way to reduce, or eliminate, use of an external frame buffer in displaying images, and thus reduces power consumed by use of the frame buffer in displaying images and/or reducing a bandwidth of image data being received into the electronic display 18. In some cases, an internal framebuffer (e.g., located in the electronic display 18, such as in a display driver integrated circuit of the electronic display 18) may be used in lieu of or in addition to memory-in-pixel techniques. By implementing memoryin-pixel or related techniques, an electronic display 18 may be programmed with smaller bandwidths of image data, further enabling power consumption savings. In addition, an electronic display 18 using memory in the pixel or in an onboard frame buffer may have a less complex design than an electronic display 18 without memory in the pixel or without an onboard framebuffer. These benefits may be realized because a pixel retains data transmitted to its memory until new image data is written to the memory.

[0061] Similarly, portions of image data may program a subset of pixels associated with the electronic display 18 at a time. An image to be displayed is typically converted into numerical data, or image data, so that the image is interpretable by components of the electronic display 18. In this way, image data itself may be divided into small "pixel" portions, each of which may correspond to a pixel portion of the electronic display 18, or of a display panel corresponding to the electronical display 18. In some embodiments, image data is represented through combinations of red-green-blue light such that one pixel appearing to have a single color is really three sub-pixels respectively emitting a proportion of red, green, and blue light to create the single color. In this way, numerical values, or image data, that quantify the combinations of red-green-blue light may correspond to a digital luminance level, or a gray level, that associates a luminance intensity (e.g., a brightness) of a color of the image data for those particular sub-pixels. As will be appreciated, the number of gray levels in an image usually depends on a number of bits used to represent the gray levels in a particular electronic display 18, which may be expressed as  $2^N$  gray levels where N corresponds to the number of bits used to represent the gray levels. By way of example, in an embodiment where an electronic display 18 uses 8 bits to represent gray levels, the gray level ranges from 0, for black or no light, to 255, for maximum light and/or full light, for a total of 256 potential gray levels. Similarly, an electronic display 18 using 6 bits may use 64 gray levels to represent a luminance intensity for each sub-pixel.

[0062] Having memory in the pixels of an electronic display 18 enables image data to transmit to sub-pixels associated with one color without image data having to transmit to additional sub-pixels associated with a second color at the same time. For the purposes of this disclosure, sub-pixels are discussed in terms of red-green-blue color

channels, where a color channel is a layer of image data including gray levels for a single color where when combined with additional color channels creates an image of a true, or desired, color, and where the image data for a color channel corresponds to image data transmitted to a sub-pixel for the color channel. However, it should be understood that any combination of color channels and/or sub-pixels may be used, such as, blue-green-red, cyan-magenta-yellow, and/or cyan-magenta-yellow-black.

[0063] To help illustrate, a display system 50 associated with an electronic display 18 that does not implement memory-in-pixel and a display system 52 associated with an electronic display 18 that does implement memory-in-pixel, which may each respectively be implemented in an electronic device 10, is shown in FIG. 5. The display system 50 includes a timing controller 54 to receive image data 56, a frame buffer 58, a row driver 60 and a column driver 62 communicatively coupled through communicative link 64 to the timing controller 54, and a pixel array 66 that receives control signals from the column driver 62 and the row driver 60 to create an image on an electronic display 18. Furthermore, the display system 52 includes a timing controller 54 to receive image data 56, a row driver 60 and a column driver 62 communicatively coupled through a communicative link 68 to the timing controller 54, and a pixel array 69 implementing memory-in-pixel techniques that receives control signals from the column driver 62 and the row driver 60 to create an image on an electronic display 18.

[0064] In preparing to display an image, the display system 50 may receive the image data 56 at the timing controller 54. The timing controller 54 may receive and use the image data 56 to determine clock signals and/or control signals to control a provision of the image data 56 to the pixel array 66 through the column driver 62 and the row driver 60. Additionally or alternatively, in some embodiments, the image data 56 is received by the frame buffer 58. [0065] In either case, the frame buffer 58 may serve as external storage for the timing controller 54 to store the image data 56 prior to output to the column driver 62 and/or the row driver 60. The timing controller 54 may transmit the image data 56 from the frame buffer 58 to the column driver 62 and/or the row driver 60 through the communicative link 64.

[0066] The communicative link 64 is large enough (e.g., determined through transmission bandwidth of image data) to simultaneously transmit image data 56 associated with all the channels to the row driver 60 and/or the column driver 62, for example, the image data 56 associated with a red channel, a green channel, and a blue channel. In this way, the communicative link 64 communicates image data 56 associated with a respective pixel of the pixel array 66 for the red channel, the green channel, and the blue channel at the same time. The column driver 62 and the row driver 60 may transmit control signals based on the image data 56 to the pixel array 66. In response to the control signals, the pixel array 66 emits light at varying luminosities, or brightness indicated through gray levels ranging from, for example, 0 to 255, to communicate an image.

[0067] However, the display system 52 receives the image data 56 at the timing controller 54. The timing controller 54 may use the image data 56 to determine clock signals used to provision the image data 56 to the memory-in-pixel pixel array 69. The timing controller 54 transmits the image data 56 to the row driver 60 and/or the column driver 62 to

program the memory of the pixel array 69 with digital data signals associated with the image data 56, where the digital data signals indicate the emission brightness/gray level for the pixels of the pixel array 69.

[0068] By implementing memory-in-pixel systems and methods, the display system 52 may reduce a bandwidth of signals communicated over communicative link 68, for example, when compared to a bandwidth of signals communicated over the communicative link 64. In some instances, a single channel of image data 56 may transmit through the communicative link 64 (e.g., red channel), as opposed to all channels being simultaneously transmitted to the pixel array 66 (e.g., red-green-blue channels). In this way, the communicative link 68 communicates image data 56 associated with a respective pixel of the pixel array 66 for the red channel, the green channel, and the blue channel at different times, causing a decrease in an overall bandwidth of signals used to communicate image data 56. Decreasing an overall bandwidth of the communicative link 68 may lead to a decrease in power consumption of the electronic device 10 because processing less data (e.g., a single channel of image data) at a given time may consume fewer processing resources than processing more data (e.g., three channels of

[0069] To elaborate on operating the pixel array 69 with memory-in-pixel to display images, an example of a display system 52A implementing memory-in-pixel having a timing controller 54 linked through communicative link 68 to a row driver 60 and/or a column driver 62, is shown in FIG. 6. The display system 52A includes a pixel array 69 of L rows by M columns with one or more pixels 70 each having subpixels 72 corresponding to color channels of the electronic display 18, for example, a red sub-pixel 72R, a green sub-pixel 72G, and a blue sub-pixel 72B, where each of the sub-pixels 72 includes a memory 78 to store up to N bits and a driver (DRV) 80 to operate the sub-pixel 72 to emit light, is shown in FIG. 6. It should be appreciated that the depicted display system 52A is merely intended to be illustrative and not limiting. For example, in some embodiments, the pixel array 69 may include sub-pixels 72 to emit various amounts of cyan, yellow, and magenta light corresponding to cyanyellow-magenta color channels instead of, or in addition to, the red-green-blue color channels.

[0070] Explaining operation of the display system 52A, the timing controller 54 receives image data 56 corresponding to a next image to be displayed on an electronic display having the pixel array 69. The timing controller 54 generates control signals and/or clocking signals responsive to the image data 56 and transmits signals related to operating rows of pixels 70 to the row driver 60 and transmits signals related to operating columns of pixels 70 to column driver 62. The row driver 60 is responsive to the signals associated with the image data 56 transmitted from the timing controller 54 and generates emit control signals 82 and write control signals 84 for each red-green-blue (RGB) channel. The column driver 62, also being responsive to the signals associated with the image data 56 transmitted from the timing controller 54, generates image data 86 to be transmitted to the memory 78 of each of the pixels 70. The column driver 62 may generate image data 86 in response to the signals associated with the image data 56 and/or the image data 56, in some embodiments, however, image data 56 transmits to each of the pixels 70 as image data 86. The column driver 62 generates data of size N bits for each sub-pixel 72, matching a size of the memory 78 which is also size N bits.

[0071] Generally, through transmission of the emit control signals 82, the write control signals 84, and the image data 86, the pixels 70 are operated to emit light to create an image on an electronic display 18. Each of the pixels 70 receives a respective emit control signal 88 of the emit control signals 82 transmitted from the row driver 60, a respective three write control signals 90 of the write control signals 84, and respective image data 92 for the channels of the pixel 70, for example, N bits of image data for the red channel (image data—R) 92R, N bits of image data for the green channel (image data—G) 92G, and N bits of image data for the blue channel (image data—B) 92B. The write control signals 84 may enable a memory 78 of the pixel 70 to be programmed by the image data 86 transmitted by the column driver 62. In addition, a respective emit control signal 88 of the emit control signals 82 may control if the pixel 70 is able to emit light. The emit control signal 88 transmits to respective pixels 70 of a column. An enabled emit control signal 88 may activate a driver 80 causing digital image data 92 from a memory 78 to transmit to a light-emitting portion of the pixel 70, for example, a light-emitting diode associated (LED) with a sub-pixel 72, that uses analog data signals to cause light emitted from the pixel 70. In the depicted embodiment, columns of pixels 70, for example, pixels 70 R1C1, R2C1, R3C1, to RLC1 in a first column receive a same emit control signal 88. Image data 92 transmitted to a pixel 70 causes the pixel 70 to emit light of an overall color and/or brightness.

[0072] A perceived color emitted from the pixel 70 changes based on the light emitted from each of the three channels of the pixel 70, that is, the light emitted from each respective sub-pixel. For example, operating each sub-pixel to output a brightness of 0, causes the pixel 70 to appear to be off while operating a red sub-pixel 72R to output a brightness of 100%, a green sub-pixel 72G to output a brightness of 50%, and a blue sub-pixel 72B to output a brightness of 0% may cause a pixel 70 to emit an overall color that is perceived as an orange color. Thus, data is rendered and transmitted to each sub-pixel 72 to correspond to individual color channels of a pixel 70.

[0073] Implementing memory 78 in a pixel 70 enables image data 92 to be programmed into the pixel 70 prior to a desired presentation time of the image. In some embodiments, an enabled write control signal 90 causes the memory 78 to clear (or overwrite) stored image data 92, where not enabling a write control signal 90 may cause the memory 78 to retain the programmed image data 92. For example, to write new image data, a write control signal—R 90R may cause a memory 78 of a red sub-pixel 72R to clear, enabling the writing of new image data, image data—R 92R to be loaded into the memory 78. In this example, a write control signal—B 90B was not enabled, thus the memory 78 of the blue sub-pixel 72B does not clear and continues to retain its programmed image data, image data—B 92B. Having memory 78 in pixels 70 is an improvement to display technologies and processing technologies because memory 78 enables portions of image data 86 to be written at a time instead of a whole frame of data, causing improved use of available bandwidth to communicate image data for display on an electronic display 18, as well as improvements to

6

power consumption used for processing image data, as explained earlier with reference to FIG. 5.

[0074] In the pixel array 69, image data 86 is communicated from the column driver 62 to the sub-pixels 72 through a direct communicative coupling, for example, through a communicative coupling 94. In some embodiments, a multiplexing circuit may be used to control transmission of image data 86 to sub-pixels 72 such that a multiplexing control signal is used by the column driver 62 to arbitrate transmission of image data 98 to a sub-pixel 72, for example, where in such arbitration a red sub-pixel 72R may not receive image data 98 at the same time as a blue sub-pixel 72B or a green sub-pixel 72G.

[0075] To elaborate, an example embodiment of a display system 52B associated with an electronic display 18 implementing memory-in-pixel including a timing controller 54 linked through communicative link 68 to a row driver 60 and a column driver 62, is shown in FIG. 7. The display system 52B, similar to the display system 52A depicted in FIG. 6, includes a pixel array 69 of L rows by M columns with one or more pixels 70 each having sub-pixels 72, for example, a red sub-pixel 72R, a green sub-pixel 72G, and a blue sub-pixel 72B, where each of the sub-pixels 72 includes a memory 78 to store up to N bits and a driver (DRV) 80 to operate the sub-pixel 72 to emit light, is shown in FIG. 6. It should be appreciated that the depicted display system 52B is merely intended to be illustrative and not limiting. It is noted functions and/or descriptions of the display system 52 that are common to both FIG. 6 and FIG. 7 are relied upon herein.

[0076] In the example embodiment of the display system 52B in FIG. 7, the pixel array 69 includes a multiplexing circuit 96 that receives image data 98 of size N bits from the column driver 62. The multiplexing circuit 96 is responsive to a respective multiplexing control signal (MUX control signal) 100 of multiplexing control signals 101. The MUX control signal 100 may cause the multiplexing circuit 96 to output data to a sub-pixel 72 of a pixel 70. In this way, the column driver 62, through emission of the MUX control signal 100, may operate to program a sub-pixel 72 (e.g., one color channel) of a pixel 70 at a time via, for example, a communicative coupling 94. For the pixel array 69, various embodiments of sub-pixel 72 circuits may be used.

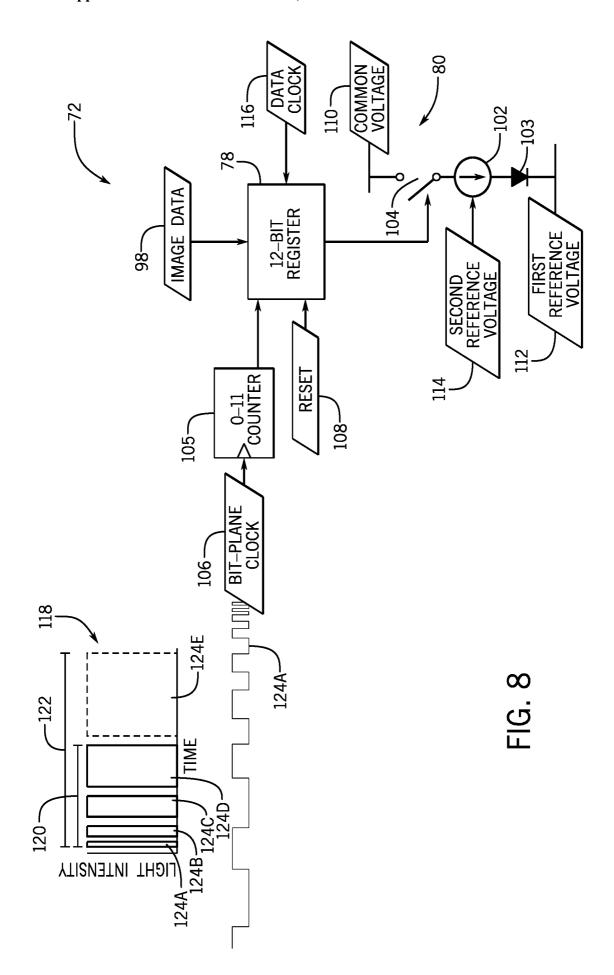

[0077] An example of an embodiment of a sub-pixel 72 implementing memory-in-pixel techniques includes a memory 78, a driver 80, a current source 102, a LED 103, a switch 104, and a counter 105, where the sub-pixel 72 receives a variety of signals including image data 98, a bit-plane clock 106, a reset signal 108, a common voltage 110, a first reference voltage 112, a second reference voltage 114, and a data clock 116, is shown in FIG. 8. It should be appreciated that the depicted sub-pixel 72 is merely intended to be illustrative and not limiting. For example, memory 78 is depicted as a 12-bit register but may be any suitable memory circuit to store any suitable number of bits.

[0078] The depicted sub-pixel 72 may emit according to a binary pulse width modulation emission scheme. To explain operation of the sub-pixel 72, image data 98 transmits to the memory 78 from, for example, a column driver 62. Additionally or alternatively, image data 92, image data 56, or any suitable image data may be transmitted to the memory 78 for storage. Upon receiving the image data 98, the memory 78 stores the image data 98 clocked in by the data clock 116. The image data 98 may be represented by binary

data such that any given bit may equal a zero, "0," or a one, "1", where a 0 corresponds to a logical low voltage value for the system and a 1 corresponds to a logical high voltage value for the system. The memory 78 may output the image data 98 to the switch 104, for example, bit by bit in order from least significant bit to most significant bit, according to a clocking signal generated by a combination of the counter 105 and the bit-plane clock 106.

[0079] As shown, a bit-plane clock 106 has clocking time periods that increase over time to correspond to a level of influence of a particular bit in the image data 98. In this way, a least significant bit of the image data 98 may be associated with a smaller clocking time period than a most significant bit of the image data 98.

[0080] When the memory 78 outputs the image data 98, for example, at a rising edge of the bit-plane clock 106, the image data 98 operates the switch 104 to open or close. A 0 bit causes the switch 104 to open, causing the LED 103 to not emit light while a 1 bit causes the switch 104 to close, causing the LED 103 to emit light. The operation of the switch 104 occurs at varying emission periods as a method to modulate emission of light from the LED 103, causing the perceived brightness of the sub-pixel 72 to change as the modulation changes. Thus, through the relationship between the image data 98 output from memory 78 and the switch 104, image data 98 equaling "0000000000" may cause the LED 103 to not emit light while image data 98 equaling "101011000111" may cause the LED 103 to be perceived as brighter. The image data 98 equaling "101011000111" may be perceived as brighter because the sub-pixel 72 operates to emit light in response to each logical high value, "1," through the value causing the switch 104 to activate permitting light to emit. The more times the switch 104 activates during an emission period, the brighter a pixel is perceived because the more light is emitted over time (e.g., light emits in response to the "1" and does not emit in response to the "0"). In this way, image data 98 may be derived from a desired gray level for the sub-pixel 72 without being an exact binary representation of the gray level. However, it should be noted that there may be scenarios where the desired gray level for the sub-pixel 72 does indeed equal the binary representation transmitted via image data 98.

[0081] When the switch 104 closes, an electrical connection is created between the common voltage 110 and the first reference voltage 112. This causes current from current source 102 to transmit through the LED 103 enabling light to emit from the sub-pixel 72. Thus, emission periods of the sub-pixel 72 may be varied to control a perceived light emitted from the sub-pixel 72, where the emission periods correspond to a bit placement (e.g., most significant bit, least significant bit) of the image data 98 stored in the memory 78 such that the closer a bit of image data 98 is to the most significant bit position, the longer an emission period corresponding to that bit of image data 98. Once the counter 105 counts up to 11, the counter 105 restarts and causes the bit-plane clock 106 to restart its clocking intervals, for example, to correspond to a next least significant bit after the last most significant bit emission period. Additionally or alternatively, in some embodiments, the second reference voltage 114 is included to alter an overall current value used to control light emitted from the LED 103. For instance, the second reference voltage 114 may increase a sensitivity of the LED 103 to current changes such that a lower current

value may be used to cause light to emit from the LED 103, or used to enable the LED 103.

[0082] This emission scheme is generally referred to as a binary pulse width modulation emission scheme for a subpixel 72 because the image data 98 is binary data selected to modulate light emission from the sub-pixel 72 in such a way as to change a perceived brightness of the sub-pixel 72. Graph 118 depicts emission periods for a sub-pixel 72 caused by the binary pulse width modulation emission scheme. With the binary pulse width modulation emission scheme, the sub-pixel 72 is operated to change a perceived brightness of light emitted through varying emission periods of light. As depicted in the graph 118, image data 98 received by the sub-pixel 72 is represented through five bits of binary data. Thus, when the image data 98 equals 01111, the sub-pixel 72 emits light corresponds to a first range 120 having emission periods 124A for the least significant bit and emission periods 124B, 124C, and 124D for subsequent bits. In this embodiment, the least significant bit of the image data 98 from memory 78 operates the switch 104 first, hence why the least significant bit corresponds to a first emission period 124A in time. As such, in between transmission of bits to operate switch 104, emission temporarily halts, as is seen with the no emission period between the first emission period 124A and the emission period 124B. In addition, when the image data 98 equals 11111, the emission period of the sub-pixel 72 corresponds to a second range 122 that is equal to the first range 120 plus a last emission period 124E corresponding to the most significant bit (e.g., because the most significant bit is now enabled as a 1).

[0083] When following a binary pulse width modulation emission scheme, image data 98 having data of 01111 is perceived as less bright than image data 98 having data of 11111 due to how light is perceived by a viewer of the electronic display 18. This is because the more emission periods that occur during a total emission cycle (e.g., as represented by all is in the image data 98, 11111), the brighter a light emitted from a sub-pixel 72 is perceived. As such, if the sub-pixel 72 were to emit for the last emission period 124E in addition to the first range 120 (e.g., if the most significant bit of the image data 98 was a 1), the sub-pixel 72 may be perceived as brighter on an electronic display 18 than a sub-pixel 72 emitting just for the first range 120.

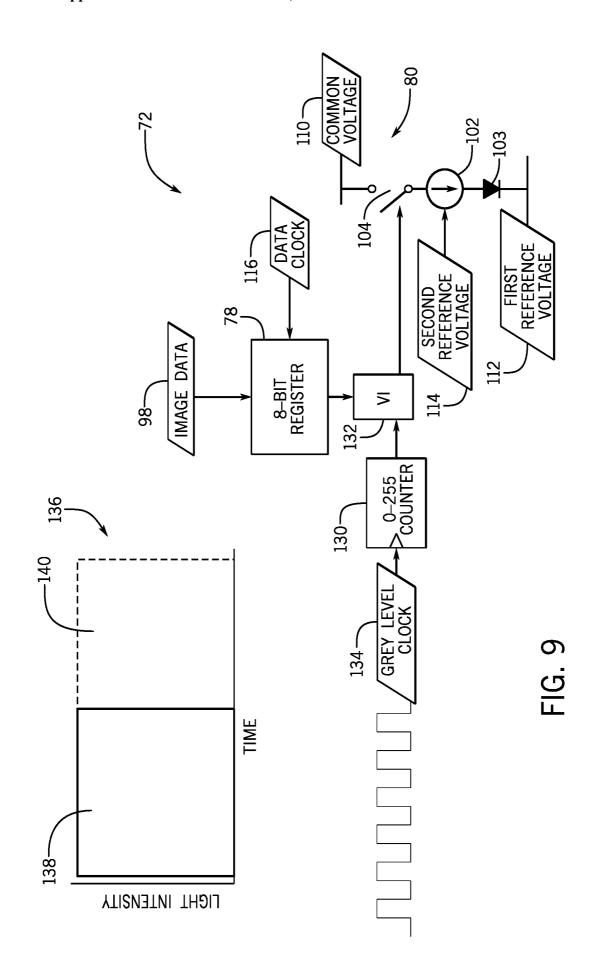

[0084] Another example of an embodiment of a sub-pixel 72 including a memory 78, a driver 80, a current source 102, a LED 103, a switch 104, a counter 130, and a comparator 132, where the sub-pixel 72 receives a variety of signals including image data 98, a gray level clock 134, a common voltage 110, a first reference voltage 112, a second reference voltage 114, and a data clock 116, is shown in FIG. 9. It should be appreciated that the depicted sub-pixel 72 is merely intended to be illustrative and not limiting. For example, memory 78 is depicted as an 8-bit register but may be any suitable memory circuit to store any suitable number of bits.

[0085] The depicted sub-pixel 72, having memory-in-pixel, may emit according to a single pulse width emission scheme. To explain operation of the sub-pixel 72, image data 98 transmits to the memory 78, for example, from a column driver 62, for storage. Additionally or alternatively, image data 92, image data 56, or any suitable image data may be transmitted to the memory 78 for storage. In some embodiments, the image data 98 may be clocked into the memory

78 by the data clock 116, for example, on a rising edge of the data clock 116. The image data 98 communicated to the sub-pixel 72 may correspond to a desired gray level at which the sub-pixel 72 is to emit light. Using the image data 98 stored in the memory 78, the comparator 132 determines if a current number represented by the counter 130 is less than or equal to the image data 98 in memory 78. In other words, the counter 130 counts up to the number indicated by the image data 98 and in response to the number represented by the counter 130 meeting a condition, for example, being smaller than or equal to the number indicated by the image data 98, the comparator 132 outputs a control signal to close the switch 104 when the condition is met. When the condition is not met, the comparator 132 does not output a control signal and opens the switch 104. Additionally or alternatively, the comparator 132 may enable a deactivation control signal to cause the opening of the switch 104. For instance, if the memory 78 stores a binary sequence of 10110101 corresponding to the number 181, the comparator 132 will check if the counter 130 has counted to the number 181, and upon the counter 130 exceeding the number 181, the comparator 132 transmits a signal to open the switch 104 thus stopping emission.

[0086] When the switch 104 closes, an electrical connection is created between the common voltage 110 and the first reference voltage 112. This causes current from current source 102 to transmit through the LED 103 causing light to emit from the sub-pixel 72. Thus, emission periods of the sub-pixel 72 may be varied to control a perceived light emitted from the sub-pixel 72 through changing a number indicated by the image data 98. Additionally or alternatively, in some embodiments, the second reference voltage 114 is included to alter an overall current value used to control light emitted from the LED 103. For instance, the second reference voltage 114 may increase a sensitivity of the LED 103 to current changes such that a lower current value may be used to cause light to emit from the LED 103, or used to enable the LED 103.

[0087] The counter 130 counts from 0 to 255 and increments based on a gray level clock 134, for example, a rising edge of the gray level clock 134. Periods of the gray level clock 134 represent the time difference between increments of the gray level for an electronic display 18, for example, a difference in emission between emitting a gray level of 100 and emitting a gray level of 101. In this way, the counter 130 counts up to the number represented by the image data 98 stored in memory 78 subsequently causing emission to occur for the time period corresponding to the desired gray level. The counter 130 may continue to count beyond the number represented by the image data 98 stored in memory 78 on to a maximum value, for example, 255, and may restart counting at a minimum value, for example, 0. Thus, in some embodiments, a counting range of the counter 130 may be defined through design of the counter 130, for example, through a number of registers and/or logical components included in the counter 130. By the time the counter 130 restarts counting at 0, additional image data 98 may be stored into memory 78 to begin comparison for a next emission period of a gray level associated with the additional image data 98.

[0088] Through following this emission scheme, the sub-pixel 72 may follow a single pulse width modulation emission scheme. A representation of an emission of light from a sub-pixel 72 following a single pulse width modulation

emission scheme is shown in graph 136. The graph 136 includes an actual emission period 138 and a total emission period 140. The total emission period 140 corresponds to a total length of emission represented by a maximum number transmitted as image data 98, for example, 255, and may correspond to a maximum perceived brightness of light emitted from the sub-pixel 72. The actual emission period 138 corresponds to a period of time a sub-pixel 72 emitted light for according to a number less than the maximum transmitted as the image data 98, for example, from a counter 130. A counter 130 increments from 0 to 255 taking the amount of time represented by the total emission period 140 while the comparator 132 enables light to emit for the amount of time represented by the actual emission period 138. In this way, a sub-pixel 72 may emit light of varying perceived brightness.

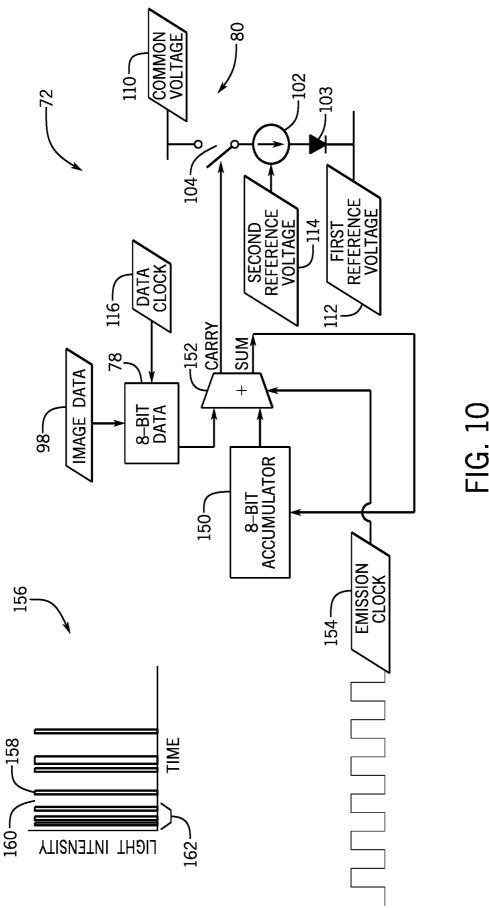

[0089] Another example of an embodiment of a sub-pixel 72 including memory 78, a driver 80, a current source 102, a LED 103, a switch 104, an accumulator 150, and an adder 152, where the sub-pixel 72 receives a variety of signals including an emission clock 154, image data 98, a common voltage 110, a first reference voltage 112, a second reference voltage 114, and a data clock 116, is shown in FIG. 10. It should be appreciated that the depicted sub-pixel 72 is merely intended to be illustrative and not limiting. For example, memory 78 is depicted as being able to store 8-bits of image data 98 but may be any suitable memory circuit to store any suitable number of bits.

[0090] The depicted sub-pixel 72, having memory-inpixel, may emit according to a pulse density modulation emission scheme. In a pulse density modulation emission scheme each pulse has a constant light emitted and a constant emission period but variable separating intervals between pulses—where a brighter light emitted from the sub-pixel 72 corresponds to a higher number of pulses during a same time period. To explain operation of the sub-pixel 72 for the pulse density modulation emission scheme, image data 98 transmits to the memory 78, for example, from a column driver 62, for storage. Additionally or alternatively, image data 92, image data 56, or any suitable image data may be transmitted to the memory 78 for storage. The image data 98 transmitted to the sub-pixel 72 is generated based at least on a desired gray level at which the sub-pixel 72 is to emit light.

[0091] Upon receiving the image data 98, the memory 78 stores the image data 98 according to the data clock 116, for example, loading bits of image data 98 bit by bit on each rising edge of the data clock 116. The memory 78 outputs the image data 98 to be added to binary data stored in the accumulator 150. While the accumulator 150 is shown as being an 8-bit accumulator, it should be understood that any suitable accumulator or register may be used to temporarily store data. The adder 152 may perform binary addition of the image data 98 and binary data of the accumulator 150 in response to an emission clock 154, for example, a rising edge of the emission clock 154. The sum from the adder 152 is transmitted for storage in the accumulator 150 for use with next image data 98 while a carry bit is used to open and/or close the switch 104.

[0092] When the switch 104 closes, an electrical connection is created between the common voltage 110 and the first reference voltage 112. This causes current from current source 102 to transmit through the LED 103 generally enabling light to emit from the sub-pixel 72. In this way,

variable separating intervals between pulses created by the emission clock 154 and the adder 152 transmitting the carry bit from the addition may contribute to change emission of light from the sub-pixel 72. Thus, intervals separating emission pulses of the sub-pixel 72 may be varied to control light emitted from the sub-pixel 72, where a brighter light may emit in response to smaller intervals separating the pulses (e.g., a higher density of pulses corresponds to a brighter perceived light emitted from LED 103). Additionally or alternatively, in some embodiments, the second reference voltage 114 is included to alter an overall current value used to control light emitted from the LED 103. For instance, the second reference voltage 114 may increase a sensitivity of the LED 103 to current changes such that a lower current value may be used to cause light to emit from the LED 103, or used to enable the LED 103.

[0093] Graph 156 depicts emission pulses and variable separating intervals between pulses caused by the pulse density modulation emission scheme. With the pulse density modulation emission scheme, the sub-pixel 72 emits pulses separated by different length of no emission intervals to change an overall light emitted from the sub-pixel 72. As depicted in graph 156, image data 98 may cause the sub-pixel to emit an emission pulse 158 and to not emit for the time period of a no-emission interval 160. For example, emission pulses 162 have a smaller no-emission interval separating respective emission pulses than the emission interval 160, and thus the LED 103 of the sub-pixel 72 may emit light for the emission pulses 162 that is perceived as brighter than a light emitted from the LED 103 due to the emission pulse 158.

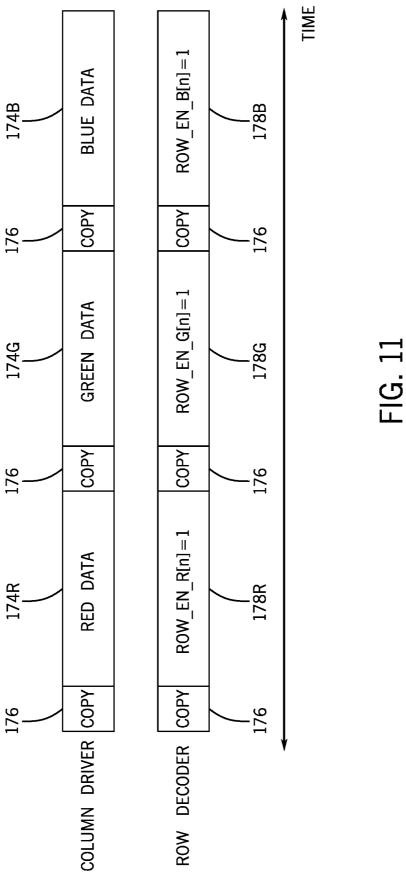

[0094] Thus, to summarize, through using memory-inpixels techniques, a timing controller 54 may program image data 98 into a display system 52 in smaller portions of image data 98 as opposed to programming image data for all sub-pixels 72 at a same time. To illustrate, a timing diagram of signal transmitted within a display system 52 to prepare to transmit image data for storage in one or more memories 78 illustrates a red image data transmission period 174R, green image data transmission period 174G, blue image data transmission period 174B, one or more copy periods 176, and one or more enable periods 178, is shown in FIG. 11.

[0095] As depicted, a column driver 62 may receive a signal to initiate the copying of red data into one or more memories 78 of one or more red sub-pixels 72R. Upon receiving the signal, the column driver 62 may enter a copy period 176 to prepare for transmitting red data to the red sub-pixels 72R. During the copy period 176, the column driver 62, for example, via internal circuitry such as a row decoder, may prepare to enable multiplexing circuits 96 associated with pixels 70 of a display system 52. The column driver 62, or other suitable circuitry, may operate the multiplexing circuits 96 to permit the programming of memories 78 of red sub-pixels 72R and may operate the multiplexing circuits 96 to not permit the programming of memories 78 of blue sub-pixels 72B and green sub-pixels 72G, for example, through enabling and/or disabling multiplexing control signals 101. In this way, the red image data may be transmitted and stored in the memories 78 corresponding to red sub-pixels 72R. At the end of the copy period 176, the column driver 62 may transmit red image data to the red sub-pixels 72R during the red image data transmission period 174R. The transmitted red image data is transmitted

into the respective memories 78 of the red sub-pixels 72R to be programmed with new red image data. Upon transmitting the red image data to the red sub-pixels 72R, the column driver 62 and the row decoder may repeat the described process for green image data and blue image data, enabling selective programming of the various color channels associated with each pixel 70.

[0096] Generally, a sub-pixel 72 is operated to emit light through receiving one or more control signals, such as, from the column driver 62 and/or the row driver 60. The row driver 60 and the column driver 62 may control operation of the sub-pixel 72 by using control signals to control components of the sub-pixel 72, such as a current drive of the sub-pixel 72. As described above, the column driver 62 may be responsible at least for the transmission of image data to the sub-pixel 72 while the row driver 60 may be responsible for one or more control signals to control emission that transmit to the sub-pixel 72. The sub-pixel 72 may include any suitable controllable element responsive to these control signals and image data, such as a transistor, one example of which is a metal-oxide-semiconductor field-effect transistor (MOSFET). However, any other suitable type of controllable elements, including thin film transistors (TFTs), p-type and/or n-type MOSFETs, and other transistor types, may also be used.

[0097] In some embodiments, the row driver 60 and/or column driver 62 may perform an initialization process, a charging process, a programming process, and an emission process to the sub-pixel 72 to prepare to display an image on an electronic display 18. Through performing these processes, a row driver 60 and/or a column driver 62 of the electronic display 18 may initialize the sub-pixel 72 to be programmed, may charge a capacitor for programming, may program the sub-pixel 72 with signals corresponding to a driving current designed to cause the sub-pixel 72 to emit light, and may enable image data to control emission of light from the sub-pixel 72. In some embodiments, a current drive may be responsible for generating the driving current in the sub-pixel 72.

[0098] To help elaborate on a sub-pixel circuit having a current drive, an embodiment of a sub-pixel 72 including an initialization transistor (MINI) 220, a driving transistor (MDR) 222, a selection transistor (MSEL) 224, a switching transistor (MS) 226, a reset transistor (MRST) 228, a light-emitting portion such as a LED 230, a capacitor 232, and an auto-zero transistor (MAZ) 234 is shown in FIG. 12. It should be appreciated that the depicted sub-pixel 72 is intended to be illustrative and not limiting. For example, the row driver 60 and the column driver 62 are described herein as outputting image data and control signals relevant to displaying a next image on an electronic display 18, however it should be understood that any suitable component may be used to emit control signals to perform described processes to display of the next image. Furthermore, the circuitry shown in FIG. 12 is merely an example of circuitry implemented in a sub-pixel 72 and/or a pixel 70, and should not be interpreted as limiting. For example, a voltage drive circuit (e.g., voltage drive) may be used with the sub-pixel 72 instead of a current drive circuit (e.g., current drive).

[0099] During an initialization process, a row driver 60 may enable a reset control (CSreset) signal 235 and disable an auto-zero control (CSauto.zero) signal 237. The CSreset signal 235 may transmit to the MRST 228. In response to receiving the CSreset signal 235, the MRST 228 may

activate and permit the draining of residual signals from the display of the first image from the sub-pixel 72. These residual signals may drain through to a node coupled to a voltage reset (Vreset) signal 239 designed to encourage draining of the residual signals (e.g., 0 volts), such as a system ground or a system reference voltage. In addition, the row driver 60 may enable a selection control (CSselect) signal 241. The CSselect signal 241 may transmit to the MSEL 224. In response to receiving the CSselect signal 241, the MSEL 224 may activate and permit transmission of voltage data (Vdata) signal 242 to a node of the capacitor 232. To complete the initialization process, the row driver 60 may also enable an initialization control (CSinitialization) signal 243. The CSinitialization signal 243 may transmit to the MINI 220. In response to receiving the CSinitialization signal 243, the MINI 220 may activate and permit initialization of the capacitor 232 to occur. In this state, the capacitor 232 may charge with a voltage corresponding to a voltage difference between the Vdata signal 242 and an initialization voltage (Vinitialization) signal 244. As such, the voltage difference may be programmed through selecting different values for Vdata signal 242 and Vinitialization signal 244 based on a desired voltage level to initialize the capacitor 232 with, while protecting the sub-pixel 72 from receiving additional signals that may interfere with the initialization or that may cause unintentional emissions of light from the LED 230. The row driver 60 may continue the initialization process until the row driver 60 disabled the CSinitialization signal 243 causing the MINI 220 to deac-

[0100] After the initialization process, the row driver 60 may perform the charging process while the MINI 220 and the MRST **228** are deactivated. During the charging process, the MAZ 234 and the MINI 220 remain deactivated, while the MSEL 224 remains activated. While the MSEL 224 is activated, the capacitor 232 charges based on the Vdata signal 242 and a reference voltage (Vreference) signal 246. Charging the capacitor 232 may enable a driving current to transmit through the MDR 222 even while the MSEL 224 is deactivated. In some embodiment, the capacitor 232 stores the voltage value of the Vdata signal 242 such that the MDR 222 remains activated throughout the emission processpermitting the sub-pixel 72 to produce a constant driving current through the LED 230 for emission. In this way, the sub-pixel 72 has a current drive—since the driving current enables the emission of light from the LED 230 while the MS 226 is activated.

[0101] During the programming process, the row driver 60 may enable the CSauto.zero signal 237 causing the activation of the MAZ 234. When the MAZ 234 activates, an electrical coupling is formed between the node of the capacitor 232 and a source node of the MS 226, such that a voltage value of the source node of the MS 226 increases to equal the voltage value of a gate voltage (Vg) 245 of MDR 222. After period of time sufficient for the voltage of source node of the MS 226 to increase to equal the voltage value of Vg 245, the row driver 60 may disable the CSauto.zero signal 237 causing the MAZ 234 to deactivate. At this state, the sub-pixel 72 is programmed with electrical signals ready to transmit through to the LED 230 upon activation of the MS 226. That is, at this state, the sub-pixel 72 is ready to transmit a driving current created through the programmed signals in response to CSimage.data signal 247 enabling the MS 226.

[0102] Upon completion of the programming process, the row driver 60 may operate the sub-pixel 72 to perform the emission process. During the emission process, the sub-pixel 72 emits light according to image data control (CSimage. data) signal 247 transmitted to the MS 226, for example, from the column driver 62. The sub-pixel 72 may receive the CSimage.data signal 247 from any suitable component of an electronic device 10 that may create and/or generate image data for display via a sub-pixel 72. The MS 226 activates in response to an enabled CSimage.data signal 247, for example, a logical high bit of a voltage having sufficient value to switch the MS 226 (e.g., large enough to overcome the programmed voltage at the source node of the MS 226 and a threshold voltage of the MS 226). Upon activation of the MS 226, the voltage stored at the source node of the MS 226 transmits as a driving current through the LED 230. If the driving current exceeds a threshold voltage of the LED 230, where the threshold voltage of an LED represents a voltage value at or above which light emits from the LED, thus the LED 230 may emit light based at least in part on a value of the driving current.

[0103] As will be appreciated, the CSimage.data signal 247 may be binary and/or digital data representative of image data used to operate the sub-pixel 72 to emit at a particular gray level to convey an image (e.g., the second image). As discussed earlier, the sub-pixel 72 may operate according to a variety of emission schemes, and as such, the CSimage.data signal 247 transmitted to the MS 226 may vary between embodiments. However, across the embodiments, the CSimage.data signal 247 is derived from an image to be displayed on the display. Furthermore, the enabling and/or disabling of the CSimage.data signal 247 at least in part causes the LED 230 to emit light or to not emit light, and thus enables the CSimage.data signal 247 to modulate the emission of light from the sub-pixel 72.

[0104] Upon a completion of the emission process, the row driver 60 may disable the CSselect signal 241 and enable the CSreset signal 235, causing the deactivation of the MSEL 224 and the activation of the MRST 228. Upon the MSEL 224 deactivating, the sub-pixel 72 may no longer operate to emit light because the capacitor 232 is no longer receiving a charge and because residual signals from the emission process are drained permitted by the enabling of the MRST 228.

[0105] The sub-pixel 72 described is considered a current drive pixel because the sub-pixel 72 has a primary current that drives the LED 230 to emit light or not emit light. The primary, or driving, current transmits through MS 226 in response to various control signals controlling the timing of the light emission from the sub-pixel 72. The described sub-pixel 72 circuit may have particular advantages including how a digital output is able to control emission from the LED 230 without further conversion into an analog output. In addition, inclusion of a capacitor 232 may enable compensation for a change of threshold voltage associated with the sub-pixel 72 from a substrate bias effect, a side effect associated with applying a voltage to a gate of some transistors

[0106] Further improvements to the sub-pixel 72 may occur if a voltage drive is included in addition to the current drive structure of sub-pixel 72 in FIG. 12. At the beginning of the emission process, the voltage drive is enabled for a period of time to provide a boost to the anode of the LED 230 to make initial emission of light easier, where a lower

driving current may be used to enable light emission than without boosting the anode of the LED 230. A smaller driving current value may be used to drive the LED 230 to emit light because the LED 230 may operate in a forward bias region, or an operating region of an LED 230 more sensitive to small changes in currents, because of the boost provided by the voltage drive.

[0107] To illustrate, a second embodiment of the sub-pixel 72 having a hybrid drive including a current drive 270 and a voltage drive 272 and having a memory 78 is shown in FIG. 13. It should be appreciated that the depicted sub-pixel 72 is intended to be illustrative and not limiting. For example, the current drive 270 and the voltage drive 272 are shown as separate elements in the sub-pixel 72 but one or both of the drives may be included in the driver 80 described earlier.

[0108] A row driver 60 and/or a column driver 62 may operate the sub-pixel 72 to emit light by enabling and/or disabling control signals. The row driver 60 and/or the column driver 62 may use the control signals to perform various processes to cause the sub-pixel 72 to emit light, including an initialization process, a charging process, a programming process, and an emission process for the sub-pixel 72 to enable display of the image data corresponding to an image to be displayed.

[0109] To help illustrate the interaction of control signals emitted by the row driver 60 and/or the column driver 62 and the sub-pixel 72 of FIG. 13, a timing diagram 279 corresponding to signals used to display including a Vdata signal 242, a CSinitialization signal 243, a CSselect signal 241, a CSauto.zero signal 237, an CSimage.data signal 247, a CSselect signal 280, and a CSreset signal 235, is shown in FIG. 14. It should be appreciated that the timing diagram is intended to be illustrative and not limiting, for example, control signals shown in FIG. 14 may represent more or less control signals than implemented in a sub-pixel 72.

[0110] The initialization process described above corresponds to a time period 282. During the time period 282, a row driver 60 may provide a high voltage for the Vdata signal 242, may enable the CSinitialization signal 243 for the duration of the initialization process, may enable the CSselect signal 241 for a time period 284, may disable the CSauto.zero signal 237, may disable the CSreset signal 235, and may disable the CSselect signal 280.

[0111] Referring back to FIG. 13, the control signals outputted by the row driver 60 to execute an initialization process cause activation and/or deactivation of various switching elements, as described earlier. Implementing the control signals of FIG. 14 into the sub-pixel 72 causes a MINI 220 to activate in response to the enabled CSinitialization signal 243, causes a MSEL 224 to activate in response to the enabled CSselect signal 241, causes a MAZ 234 to deactivate in response to the disabled CSauto.zero signal 237, causes a MRST 228 to deactivate in response to the disabled CSreset signal 235, and causes a voltage drive switching element (MVD) 285 to deactivate in response to the disabled CSselect signal 280. This arrangement enables a difference in voltage values between the Vdata signal 242 and the Vinitialization signal 244 to charge a capacitor 232. The row driver 60 may continue the initialization process until the row driver 60 disables the CSinitialization signal 243 to cause the MINI 220 to deactivate, and thus end initialization.

[0112] Referring back to FIG. 14, the timing diagram 279 shows, after the initialization process, the row driver 60 disables the CSinitialization signal 243 to perform a charging process to the sub-pixel 72. During the charging process, the Vdata signal 242, the CSauto.zero signal 237, the CSimage.data signal 247, the CSselect signal 280, and the CSreset signal 235 remain at their previous state. The timing diagram 279 shows the Vdata signal 242 at a high voltage level for the sub-pixel 72 circuit (DVDD), for example, corresponding to a logical high value in binary data for the sub-pixel 72 and/or the electronic device 10. In some embodiments, DVDD is equal to a voltage value of the Vreference signal 246.

[0113] Referring back to FIG. 13, the control signals outputted by the row driver 60 activate and/or deactivate various switching elements to execute a charging process. Upon the disabling of the CSinitialization signal 243 and the deactivation of the MINI 220, the capacitor 232 charges based on the Vdata signal 242 and the Vreference signal 246. Charging the capacitor 232 may enable the current drive 270 to remain in use during the emission process even while the MSEL 224 is deactivated. In some embodiments, the capacitor 232 holds the voltage value of the Vdata signal 242 after the charging process such that the MDR 222 may remain activated throughout the emission process—permitting the current drive 270 to produce a constant driving current through the LED 230 for emission.

[0114] After a set period of time suitable to charge the capacitor 232, the row driver 60 may perform a programming process. Referring briefly to FIG. 14, to perform the programming process, the row driver 60 enables the CSauto. zero signal 237 for a time period 286 and holds CSinitialization signal 243, the Vdata signal 242, the CSimage.data signal 247, the CSselect signal 280, and the CSreset signal 235 at their previous state. As is shown, the row driver 60 also transmits a ground voltage (GND) as the Vdata signal 242 for a time period 288 during the programming process. The GND may equal zero volts or any suitable ground reference voltage associated with an electronic display 18, an electronic device 0, and/or a sub-pixel 72.

[0115] Returning to FIG. 13, in response to the enabled CSauto.zero signal 237, the MAZ 234 activates. When the MAZ 234 activates, an electrical coupling is formed between the node of the capacitor 232 and a source node of the MS 226, such that a voltage value of the source node of the MS 226 increases to equal the voltage value of Vg 245. After the time period 286, the row driver 60 disables the CSauto.zero signal 237 and the MAZ 234 deactivates. At this state, the sub-pixel 72 is programmed with electrical signals ready to transmit to the LED 230 upon activation of the MS 226. That is, at this state, the sub-pixel 72 is ready to transmit a driving current created through the programmed signals in response to CSimage.data signal 247 enabling the MS 226. Once the source node of the MS 226 is programmed with the Vg 245 voltage, the row driver 60 transmits a Vdata signal 242 equal to GND and, at the end of the time period 284, disables the CSselect signal 241 causing the MSEL 224 to deactivate. Upon the completion of the programming process, the row driver 60 may enable and/or disable control signals to perform an emission pro-

[0116] Referring to FIG. 14, during an emission process, the row driver 60 may return a Vdata signal 242 to DVDD, may continue to disable the CSinitialization signal 243, may

continue to disable the CSselect signal 241, may enable the CSimage.data signal 247 for a time period 290, may enable the CSselect signal 280 for a time period 292, and may continue to disable the CSreset signal 235. As is illustrated, the CSselect signal 280 is enabled at the same time as the CSimage.data signal 247, however is disabled earlier than the CSimage.data signal 247. This is because the CSselect signal 280 acts to activate a switching element to provide the boost to an anode of an LED 230 of the sub-pixel 72.

[0117] Returning to FIG. 13 to illustrate, a voltage drive switching element (MVD) 285 of the sub-pixel 72 activates in response to the enabling of the CSselect signal 280 causing the voltage drive 272 to activate. In response to the MVD 285 activating, a reference voltage (Vreference) signal 300 transmits to the anode of the LED 230 upon the CSimage.data signal 247 enabling a switching transistor (MS) 302 and the MS 226 for a first transmitted CSimage. data signal 247. This causes the Vreference signal 300 to transmit at the anode of the LED 230 enabling, or "boosting," a smaller programmed value from the source of the MS 226 to cause emission of light from the LED 230. The boosting may continue for the time period 292, where upon the ending of the time period 292, the row driver 60 disables the CS select signal 280 causing the deactivating of the MVD 285 and of the MS 302.

[0118] Generally, the emission process may continue for the time period 290 with the boost lasting for a shorter time period, for example, a time period 292. During the emission process, the sub-pixel 72 is programmed to transmit the driving current through the LED 230 in response to the activation of the MS 226. As described earlier, the memory 78 of the sub-pixel 72 stores digital data and outputs digital data. Through the described hybrid drive, stored digital data is transmitted from memory 78 as digital data turning into a control signal to control the emission of light from the sub-pixel 72 with little overhead and no increased consumption of power. At the conclusion of boosting, in some embodiments, the sub-pixel 72 may be reset via enabling of the CSreset signal 235, for a duration such as time period 294. Thus, light emitted from the LED 230 may follow a variety of emission schemes, as explained earlier with FIG. **8-**FIG. **10**, to communicate gray levels associated with an image because the binary data outputted from the memory 78 acts to modulate the light emitted via the LED 230.

[0119] To help illustrate effects of the "boost" to an anode voltage of a sub-pixel 72, a graph 348 illustrating an example CSimage.data signal 350, a voltage signal 352 corresponding to a voltage at an anode of a LED 230, and a current signal 354 corresponding to a current through the LED 230 for a sub-pixel 72 not implementing a hybrid drive, is shown in FIG. 15. It should be appreciated that the timing diagram is intended to be illustrative and not limiting.